Function call¶

This chapter introduces support for subroutine and function calls in backend translation. A significant amount of code is required to support function calls, and it is organized using LLVM-supplied interfaces for clarity.

The chapter begins by introducing the MIPS stack frame structure, as many parts of the ABI are borrowed from it. Although each CPU has its own ABI, most RISC CPU ABIs share similar characteristics.

Section “4.5 DAG Lowering” of tricore_llvm.pdf provides insight into the lowering process. Section “4.5.1 Calling Conventions” in the same document is also a helpful reference for further understanding.

If you have difficulty understanding the stack frame illustrated in the first three sections of this chapter, you may consult the following resources: Appendix B, “Procedure Call Convention,” in Computer Organization and Design, 1st Edition [1]; “Run Time Memory” in a compiler textbook; or “Function Call Sequence” and “Stack Frame” in the MIPS ABI [3].

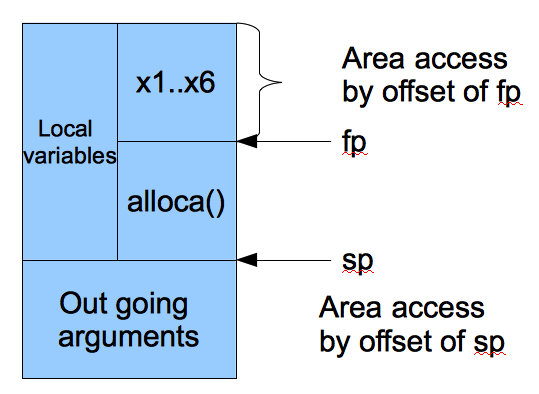

MIPS Stack Frame¶

The first step in designing Cpu0 function calls is deciding how to pass arguments. There are two options:

Pass all arguments on the stack.

Pass arguments using registers reserved for function arguments, and place any remaining arguments on the stack once the registers are full.

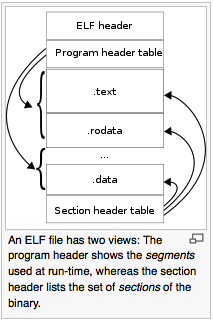

For example, MIPS passes the first four arguments in registers $a0, $a1, $a2, and $a3. Any additional arguments are passed on the stack. Fig. 39 illustrates the MIPS stack frame.

Fig. 39 Mips stack frame¶

Run llc -march=mips on ch9_1.bc, and you will get the following result.

See the comments marked with “//”.

lbdex/input/ch9_1.cpp

int gI = 100;

int sum_i(int x1, int x2, int x3, int x4, int x5, int x6)

{

int sum = gI + x1 + x2 + x3 + x4 + x5 + x6;

return sum;

}

int main()

{

int a = sum_i(1, 2, 3, 4, 5, 6);

return a;

}

118-165-78-230:input Jonathan$ clang -target mips-unknown-linux-gnu -c

ch9_1.cpp -emit-llvm -o ch9_1.bc

118-165-78-230:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llc -march=mips -relocation-model=pic -filetype=asm ch9_1.bc -o

ch9_1.mips.s

118-165-78-230:input Jonathan$ cat ch9_1.mips.s

.section .mdebug.abi32

.previous

.file "ch9_1.bc"

.text

.globl _Z5sum_iiiiiii

.align 2

.type _Z5sum_iiiiiii,@function

.set nomips16 # @_Z5sum_iiiiiii

.ent _Z5sum_iiiiiii

_Z5sum_iiiiiii:

.cfi_startproc

.frame $sp,32,$ra

.mask 0x00000000,0

.fmask 0x00000000,0

.set noreorder

.set nomacro

.set noat

# BB#0:

addiu $sp, $sp, -32

$tmp1:

.cfi_def_cfa_offset 32

sw $4, 28($sp)

sw $5, 24($sp)

sw $t9, 20($sp)

sw $7, 16($sp)

lw $1, 48($sp) // load argument 5

sw $1, 12($sp)

lw $1, 52($sp) // load argument 6

sw $1, 8($sp)

lw $2, 24($sp)

lw $3, 28($sp)

addu $2, $3, $2

lw $3, 20($sp)

addu $2, $2, $3

lw $3, 16($sp)

addu $2, $2, $3

lw $3, 12($sp)

addu $2, $2, $3

addu $2, $2, $1

sw $2, 4($sp)

jr $ra

addiu $sp, $sp, 32

.set at

.set macro

.set reorder

.end _Z5sum_iiiiiii

$tmp2:

.size _Z5sum_iiiiiii, ($tmp2)-_Z5sum_iiiiiii

.cfi_endproc

.globl main

.align 2

.type main,@function

.set nomips16 # @main

.ent main

main:

.cfi_startproc

.frame $sp,40,$ra

.mask 0x80000000,-4

.fmask 0x00000000,0

.set noreorder

.set nomacro

.set noat

# BB#0:

lui $2, %hi(_gp_disp)

ori $2, $2, %lo(_gp_disp)

addiu $sp, $sp, -40

$tmp5:

.cfi_def_cfa_offset 40

sw $ra, 36($sp) # 4-byte Folded Spill

$tmp6:

.cfi_offset 31, -4

addu $gp, $2, $25

sw $zero, 32($sp)

addiu $1, $zero, 6

sw $1, 20($sp) // Save argument 6 to 20($sp)

addiu $1, $zero, 5

sw $1, 16($sp) // Save argument 5 to 16($sp)

lw $25, %call16(_Z5sum_iiiiiii)($gp)

addiu $4, $zero, 1 // Pass argument 1 to $4 (=$a0)

addiu $5, $zero, 2 // Pass argument 2 to $5 (=$a1)

addiu $t9, $zero, 3

jalr $25

addiu $7, $zero, 4

sw $2, 28($sp)

lw $ra, 36($sp) # 4-byte Folded Reload

jr $ra

addiu $sp, $sp, 40

.set at

.set macro

.set reorder

.end main

$tmp7:

.size main, ($tmp7)-main

.cfi_endproc

From the MIPS assembly code generated above, we can see that the first four arguments are saved in registers $a0 to $a3, and the last two arguments are saved at memory locations 16($sp) and 20($sp).

Fig. 40 shows the location of the arguments in the example code ch9_1.cpp.

In the sum_i() function, argument 5 is loaded from 48($sp) because it was stored at 16($sp) in the main() function. Since the stack size of sum_i() is 32, the address of the incoming argument 5 is calculated as 16 + 32 = 48($sp).

Fig. 40 Mips arguments location in stack frame¶

The document 007-2418-003.pdf referenced in [2] is the MIPS assembly language manual. The MIPS Application Binary Interface, referenced in [3], includes the diagram shown in Fig. 39.

Load Incoming Arguments from Stack Frame¶

As discussed in the previous section, supporting function calls requires implementing an argument-passing mechanism using the stack frame.

Before proceeding with the implementation, let’s run the old version of the code in Chapter8_2/ with ch9_1.cpp and observe what happens.

118-165-79-31:input Jonathan$ /Users/Jonathan/llvm/test/

build/bin/llc -march=cpu0 -relocation-model=pic -filetype=asm

ch9_1.bc -o ch9_1.cpu0.s

Assertion failed: (InVals.size() == Ins.size() && "LowerFormalArguments didn't

emit the correct number of values!"), function LowerArguments, file /Users/

Jonathan/llvm/test/llvm/lib/CodeGen/SelectionDAG/

SelectionDAGBuilder.cpp, ...

...

0. Program arguments: /Users/Jonathan/llvm/test/build/

bin/llc -march=cpu0 -relocation-model=pic -filetype=asm ch9_1.bc -o

ch9_1.cpu0.s

1. Running pass 'Function Pass Manager' on module 'ch9_1.bc'.

2. Running pass 'CPU0 DAG->DAG Pattern Instruction Selection' on function

'@_Z5sum_iiiiiii'

Illegal instruction: 4

Since Chapter8_2/ defines LowerFormalArguments() with an empty body, we receive the error messages shown above.

Before implementing LowerFormalArguments(), we must first decide how to pass arguments in a function call.

For demonstration purposes, Cpu0 passes the first two arguments in registers by

default, which corresponds to the setting llc -cpu0-s32-calls=false.

When using llc -cpu0-s32-calls=true, Cpu0 passes all its arguments on the

stack.

The function LowerFormalArguments() is responsible for creating the incoming arguments. We define it as follows:

lbdex/chapters/Chapter9_1/Cpu0ISelLowering.h

class Cpu0TargetLowering : public TargetLowering {

/// Cpu0CC - This class provides methods used to analyze formal and call

/// arguments and inquire about calling convention information.

class Cpu0CC {

void analyzeFormalArguments(const SmallVectorImpl<ISD::InputArg> &Ins,

bool IsSoftFloat,

Function::const_arg_iterator FuncArg);

/// regSize - Size (in number of bits) of integer registers.

unsigned regSize() const { return IsO32 ? 4 : 4; }

/// numIntArgRegs - Number of integer registers available for calls.

unsigned numIntArgRegs() const;

/// Return pointer to array of integer argument registers.

const ArrayRef<MCPhysReg> intArgRegs() const;

void handleByValArg(unsigned ValNo, MVT ValVT, MVT LocVT,

CCValAssign::LocInfo LocInfo,

ISD::ArgFlagsTy ArgFlags);

/// useRegsForByval - Returns true if the calling convention allows the

/// use of registers to pass byval arguments.

bool useRegsForByval() const { return CallConv != CallingConv::Fast; }

/// Return the function that analyzes fixed argument list functions.

llvm::CCAssignFn *fixedArgFn() const;

void allocateRegs(ByValArgInfo &ByVal, unsigned ByValSize,

unsigned Align);

};

...

/// isEligibleForTailCallOptimization - Check whether the call is eligible

/// for tail call optimization.

virtual bool

isEligibleForTailCallOptimization(const Cpu0CC &Cpu0CCInfo,

unsigned NextStackOffset,

const Cpu0FunctionInfo& FI) const = 0;

/// copyByValArg - Copy argument registers which were used to pass a byval

/// argument to the stack. Create a stack frame object for the byval

/// argument.

void copyByValRegs(SDValue Chain, const SDLoc &DL,

std::vector<SDValue> &OutChains, SelectionDAG &DAG,

const ISD::ArgFlagsTy &Flags,

SmallVectorImpl<SDValue> &InVals,

const Argument *FuncArg,

const Cpu0CC &CC, const ByValArgInfo &ByVal) const;

SDValue LowerCall(TargetLowering::CallLoweringInfo &CLI,

SmallVectorImpl<SDValue> &InVals) const override;

...

}

lbdex/chapters/Chapter9_1/Cpu0ISelLowering.cpp

// addLiveIn - This helper function adds the specified physical register to the

// MachineFunction as a live in value. It also creates a corresponding

// virtual register for it.

static unsigned

addLiveIn(MachineFunction &MF, unsigned PReg, const TargetRegisterClass *RC)

{

unsigned VReg = MF.getRegInfo().createVirtualRegister(RC);

MF.getRegInfo().addLiveIn(PReg, VReg);

return VReg;

}

//===----------------------------------------------------------------------===//

// TODO: Implement a generic logic using tblgen that can support this.

// Cpu0 32 ABI rules:

// ---

//===----------------------------------------------------------------------===//

// Passed in stack only.

static bool CC_Cpu0S32(unsigned ValNo, MVT ValVT, MVT LocVT,

CCValAssign::LocInfo LocInfo, ISD::ArgFlagsTy ArgFlags,

CCState &State) {

// Do not process byval args here.

if (ArgFlags.isByVal())

return true;

// Promote i8 and i16

if (LocVT == MVT::i8 || LocVT == MVT::i16) {

LocVT = MVT::i32;

if (ArgFlags.isSExt())

LocInfo = CCValAssign::SExt;

else if (ArgFlags.isZExt())

LocInfo = CCValAssign::ZExt;

else

LocInfo = CCValAssign::AExt;

}

Align OrigAlign = ArgFlags.getNonZeroOrigAlign();

unsigned Offset = State.AllocateStack(ValVT.getSizeInBits() >> 3,

OrigAlign);

State.addLoc(CCValAssign::getMem(ValNo, ValVT, Offset, LocVT, LocInfo));

return false;

}

// Passed first two i32 arguments in registers and others in stack.

static bool CC_Cpu0O32(unsigned ValNo, MVT ValVT, MVT LocVT,

CCValAssign::LocInfo LocInfo, ISD::ArgFlagsTy ArgFlags,

CCState &State) {

static const MCPhysReg IntRegs[] = { Cpu0::A0, Cpu0::A1 };

// Do not process byval args here.

if (ArgFlags.isByVal())

return true;

// Promote i8 and i16

if (LocVT == MVT::i8 || LocVT == MVT::i16) {

LocVT = MVT::i32;

if (ArgFlags.isSExt())

LocInfo = CCValAssign::SExt;

else if (ArgFlags.isZExt())

LocInfo = CCValAssign::ZExt;

else

LocInfo = CCValAssign::AExt;

}

unsigned Reg;

// f32 and f64 are allocated in A0, A1 when either of the following

// is true: function is vararg, argument is 3rd or higher, there is previous

// argument which is not f32 or f64.

bool AllocateFloatsInIntReg = true;

Align OrigAlign = ArgFlags.getNonZeroOrigAlign();

bool isI64 = (ValVT == MVT::i32 && OrigAlign == 8);

if (ValVT == MVT::i32 || (ValVT == MVT::f32 && AllocateFloatsInIntReg)) {

Reg = State.AllocateReg(IntRegs);

// If this is the first part of an i64 arg,

// the allocated register must be A0.

if (isI64 && (Reg == Cpu0::A1))

Reg = State.AllocateReg(IntRegs);

LocVT = MVT::i32;

} else if (ValVT == MVT::f64 && AllocateFloatsInIntReg) {

// Allocate int register. If first

// available register is Cpu0::A1, shadow it too.

Reg = State.AllocateReg(IntRegs);

if (Reg == Cpu0::A1)

Reg = State.AllocateReg(IntRegs);

State.AllocateReg(IntRegs);

LocVT = MVT::i32;

} else

llvm_unreachable("Cannot handle this ValVT.");

if (!Reg) {

unsigned Offset = State.AllocateStack(ValVT.getSizeInBits() >> 3,

Align(OrigAlign));

State.addLoc(CCValAssign::getMem(ValNo, ValVT, Offset, LocVT, LocInfo));

} else

State.addLoc(CCValAssign::getReg(ValNo, ValVT, Reg, LocVT, LocInfo));

return false;

}

//===----------------------------------------------------------------------===//

// Call Calling Convention Implementation

//===----------------------------------------------------------------------===//

static const MCPhysReg O32IntRegs[] = {

Cpu0::A0, Cpu0::A1

};

//@LowerCall {

/// LowerCall - functions arguments are copied from virtual regs to

/// (physical regs)/(stack frame), CALLSEQ_START and CALLSEQ_END are emitted.

SDValue

Cpu0TargetLowering::LowerCall(TargetLowering::CallLoweringInfo &CLI,

SmallVectorImpl<SDValue> &InVals) const {

//@LowerCall {

/// LowerCall - functions arguments are copied from virtual regs to

/// (physical regs)/(stack frame), CALLSEQ_START and CALLSEQ_END are emitted.

SDValue

Cpu0TargetLowering::LowerCall(TargetLowering::CallLoweringInfo &CLI,

SmallVectorImpl<SDValue> &InVals) const {

return CLI.Chain;

}

//===----------------------------------------------------------------------===//

//@LowerFormalArguments {

/// LowerFormalArguments - transform physical registers into virtual registers

/// and generate load operations for arguments places on the stack.

SDValue

Cpu0TargetLowering::LowerFormalArguments(SDValue Chain,

CallingConv::ID CallConv,

bool IsVarArg,

const SmallVectorImpl<ISD::InputArg> &Ins,

const SDLoc &DL, SelectionDAG &DAG,

SmallVectorImpl<SDValue> &InVals)

const {

MachineFunction &MF = DAG.getMachineFunction();

MachineFrameInfo &MFI = MF.getFrameInfo();

Cpu0FunctionInfo *Cpu0FI = MF.getInfo<Cpu0FunctionInfo>();

Cpu0FI->setVarArgsFrameIndex(0);

// Assign locations to all of the incoming arguments.

SmallVector<CCValAssign, 16> ArgLocs;

CCState CCInfo(CallConv, IsVarArg, DAG.getMachineFunction(),

ArgLocs, *DAG.getContext());

Cpu0CC Cpu0CCInfo(CallConv, ABI.IsO32(),

CCInfo);

const Function &Func = DAG.getMachineFunction().getFunction();

Function::const_arg_iterator FuncArg = Func.arg_begin();

bool UseSoftFloat = Subtarget.abiUsesSoftFloat();

Cpu0CCInfo.analyzeFormalArguments(Ins, UseSoftFloat, FuncArg);

Cpu0FI->setFormalArgInfo(CCInfo.getNextStackOffset(),

Cpu0CCInfo.hasByValArg());

// Used with vargs to acumulate store chains.

std::vector<SDValue> OutChains;

unsigned CurArgIdx = 0;

Cpu0CC::byval_iterator ByValArg = Cpu0CCInfo.byval_begin();

//@2 {

for (unsigned i = 0, e = ArgLocs.size(); i != e; ++i) {

//@2 }

CCValAssign &VA = ArgLocs[i];

if (Ins[i].isOrigArg()) {

std::advance(FuncArg, Ins[i].getOrigArgIndex() - CurArgIdx);

CurArgIdx = Ins[i].getOrigArgIndex();

}

EVT ValVT = VA.getValVT();

ISD::ArgFlagsTy Flags = Ins[i].Flags;

bool IsRegLoc = VA.isRegLoc();

//@byval pass {

if (Flags.isByVal()) {

assert(Flags.getByValSize() &&

"ByVal args of size 0 should have been ignored by front-end.");

assert(ByValArg != Cpu0CCInfo.byval_end());

copyByValRegs(Chain, DL, OutChains, DAG, Flags, InVals, &*FuncArg,

Cpu0CCInfo, *ByValArg);

++ByValArg;

continue;

}

//@byval pass }

// Arguments stored on registers

if (ABI.IsO32() && IsRegLoc) {

MVT RegVT = VA.getLocVT();

unsigned ArgReg = VA.getLocReg();

const TargetRegisterClass *RC = getRegClassFor(RegVT);

// Transform the arguments stored on

// physical registers into virtual ones

unsigned Reg = addLiveIn(DAG.getMachineFunction(), ArgReg, RC);

SDValue ArgValue = DAG.getCopyFromReg(Chain, DL, Reg, RegVT);

// If this is an 8 or 16-bit value, it has been passed promoted

// to 32 bits. Insert an assert[sz]ext to capture this, then

// truncate to the right size.

if (VA.getLocInfo() != CCValAssign::Full) {

unsigned Opcode = 0;

if (VA.getLocInfo() == CCValAssign::SExt)

Opcode = ISD::AssertSext;

else if (VA.getLocInfo() == CCValAssign::ZExt)

Opcode = ISD::AssertZext;

if (Opcode)

ArgValue = DAG.getNode(Opcode, DL, RegVT, ArgValue,

DAG.getValueType(ValVT));

ArgValue = DAG.getNode(ISD::TRUNCATE, DL, ValVT, ArgValue);

}

// Handle floating point arguments passed in integer registers.

if ((RegVT == MVT::i32 && ValVT == MVT::f32) ||

(RegVT == MVT::i64 && ValVT == MVT::f64))

ArgValue = DAG.getNode(ISD::BITCAST, DL, ValVT, ArgValue);

InVals.push_back(ArgValue);

} else { // VA.isRegLoc()

MVT LocVT = VA.getLocVT();

// sanity check

assert(VA.isMemLoc());

// The stack pointer offset is relative to the caller stack frame.

int FI = MFI.CreateFixedObject(ValVT.getSizeInBits()/8,

VA.getLocMemOffset(), true);

// Create load nodes to retrieve arguments from the stack

SDValue FIN = DAG.getFrameIndex(FI, getPointerTy(DAG.getDataLayout()));

SDValue Load = DAG.getLoad(

LocVT, DL, Chain, FIN,

MachinePointerInfo::getFixedStack(DAG.getMachineFunction(), FI));

InVals.push_back(Load);

OutChains.push_back(Load.getValue(1));

}

}

//@Ordinary struct type: 1 {

for (unsigned i = 0, e = ArgLocs.size(); i != e; ++i) {

// The cpu0 ABIs for returning structs by value requires that we copy

// the sret argument into $v0 for the return. Save the argument into

// a virtual register so that we can access it from the return points.

if (Ins[i].Flags.isSRet()) {

unsigned Reg = Cpu0FI->getSRetReturnReg();

if (!Reg) {

Reg = MF.getRegInfo().createVirtualRegister(

getRegClassFor(MVT::i32));

Cpu0FI->setSRetReturnReg(Reg);

}

SDValue Copy = DAG.getCopyToReg(DAG.getEntryNode(), DL, Reg, InVals[i]);

Chain = DAG.getNode(ISD::TokenFactor, DL, MVT::Other, Copy, Chain);

break;

}

}

//@Ordinary struct type: 1 }

// All stores are grouped in one node to allow the matching between

// the size of Ins and InVals. This only happens when on varg functions

if (!OutChains.empty()) {

OutChains.push_back(Chain);

Chain = DAG.getNode(ISD::TokenFactor, DL, MVT::Other, OutChains);

}

return Chain;

}

// @LowerFormalArguments }

//===----------------------------------------------------------------------===//

void Cpu0TargetLowering::Cpu0CC::

analyzeFormalArguments(const SmallVectorImpl<ISD::InputArg> &Args,

bool IsSoftFloat, Function::const_arg_iterator FuncArg) {

unsigned NumArgs = Args.size();

llvm::CCAssignFn *FixedFn = fixedArgFn();

unsigned CurArgIdx = 0;

for (unsigned I = 0; I != NumArgs; ++I) {

MVT ArgVT = Args[I].VT;

ISD::ArgFlagsTy ArgFlags = Args[I].Flags;

if (Args[I].isOrigArg()) {

std::advance(FuncArg, Args[I].getOrigArgIndex() - CurArgIdx);

CurArgIdx = Args[I].getOrigArgIndex();

}

CurArgIdx = Args[I].OrigArgIndex;

if (ArgFlags.isByVal()) {

handleByValArg(I, ArgVT, ArgVT, CCValAssign::Full, ArgFlags);

continue;

}

MVT RegVT = getRegVT(ArgVT, IsSoftFloat);

if (!FixedFn(I, ArgVT, RegVT, CCValAssign::Full, ArgFlags, CCInfo))

continue;

#ifndef NDEBUG

dbgs() << "Formal Arg #" << I << " has unhandled type "

<< EVT(ArgVT).getEVTString();

#endif

llvm_unreachable(nullptr);

}

}

void Cpu0TargetLowering::Cpu0CC::handleByValArg(unsigned ValNo, MVT ValVT,

MVT LocVT,

CCValAssign::LocInfo LocInfo,

ISD::ArgFlagsTy ArgFlags) {

assert(ArgFlags.getByValSize() && "Byval argument's size shouldn't be 0.");

struct ByValArgInfo ByVal;

unsigned RegSize = regSize();

unsigned ByValSize = alignTo(ArgFlags.getByValSize(), RegSize);

Align Alignment = std::min(std::max(ArgFlags.getNonZeroByValAlign(), Align(RegSize)),

Align(RegSize * 2));

if (useRegsForByval())

allocateRegs(ByVal, ByValSize, Alignment.value());

// Allocate space on caller's stack.

ByVal.Address = CCInfo.AllocateStack(ByValSize - RegSize * ByVal.NumRegs,

Alignment);

CCInfo.addLoc(CCValAssign::getMem(ValNo, ValVT, ByVal.Address, LocVT,

LocInfo));

ByValArgs.push_back(ByVal);

}

unsigned Cpu0TargetLowering::Cpu0CC::numIntArgRegs() const {

return IsO32 ? array_lengthof(O32IntRegs) : 0;

}

const ArrayRef<MCPhysReg> Cpu0TargetLowering::Cpu0CC::intArgRegs() const {

return makeArrayRef(O32IntRegs);

}

llvm::CCAssignFn *Cpu0TargetLowering::Cpu0CC::fixedArgFn() const {

if (IsO32)

return CC_Cpu0O32;

else // IsS32

return CC_Cpu0S32;

}

void Cpu0TargetLowering::Cpu0CC::allocateRegs(ByValArgInfo &ByVal,

unsigned ByValSize,

unsigned Align) {

unsigned RegSize = regSize(), NumIntArgRegs = numIntArgRegs();

const ArrayRef<MCPhysReg> IntArgRegs = intArgRegs();

assert(!(ByValSize % RegSize) && !(Align % RegSize) &&

"Byval argument's size and alignment should be a multiple of"

"RegSize.");

ByVal.FirstIdx = CCInfo.getFirstUnallocated(IntArgRegs);

// If Align > RegSize, the first arg register must be even.

if ((Align > RegSize) && (ByVal.FirstIdx % 2)) {

CCInfo.AllocateReg(IntArgRegs[ByVal.FirstIdx]);

++ByVal.FirstIdx;

}

// Mark the registers allocated.

for (unsigned I = ByVal.FirstIdx; ByValSize && (I < NumIntArgRegs);

ByValSize -= RegSize, ++I, ++ByVal.NumRegs)

CCInfo.AllocateReg(IntArgRegs[I]);

}

As reviewed in the section “Global variable” [4], we handled global variable translation by first creating the IR DAG in LowerGlobalAddress(), and then completing instruction selection based on the corresponding machine instruction DAGs in Cpu0InstrInfo.td.

LowerGlobalAddress() is called when llc encounters a global variable access. Similarly, LowerFormalArguments() is called when entering a function.

Before entering the “for loop”, it gathers incoming argument information using CCInfo(CallConv, …, ArgLocs, …).

In ch9_1.cpp, the function sum_i(…) has 6 arguments. Thus, ArgLocs.size() is 6, with each argument’s information stored in ArgLocs[i].

If VA.isRegLoc() returns true, the argument is passed via register.

If VA.isMemLoc() returns true, the argument is passed via memory stack.

For register-passed arguments, the register is marked as “live-in”, and the value is copied directly from the register.

For stack-passed arguments, a stack offset is created for the frame index object. A load node is then created using this offset and added to the InVals vector.

When using llc -cpu0-s32-calls=false, the first two arguments are passed in

registers, and the remaining arguments are passed in the stack frame.

When using llc -cpu0-s32-calls=true, all arguments are passed in the stack

frame.

Before handling arguments, analyzeFormalArguments() is called. Inside it, fixedArgFn() is used to return the function pointer to either CC_Cpu0O32() or CC_Cpu0S32().

ArgFlags.isByVal() will be true for “struct pointer byval” arguments, such as %struct.S* byval in tailcall.ll.

With llc -cpu0-s32-calls=false, the stack offset begins at 8 (to allow space

in case argument registers are spilled). With llc -cpu0-s32-calls=true, the

stack offset begins at 0.

For example, when running ch9_1.cpp with llc -cpu0-s32-calls=true

(memory stack only), LowerFormalArguments() will be called twice:

First, for sum_i(), it will create six load DAGs for the six incoming arguments.

Second, for main(), no load DAG is created, as there are no incoming arguments.

In addition to LowerFormalArguments(), we use loadRegFromStackSlot() (defined in an earlier chapter) to generate the machine instruction “ld $r, offset($sp)”, which loads arguments from the stack frame.

GetMemOperand(…, FI, …) returns the memory location of the frame index variable, representing the offset.

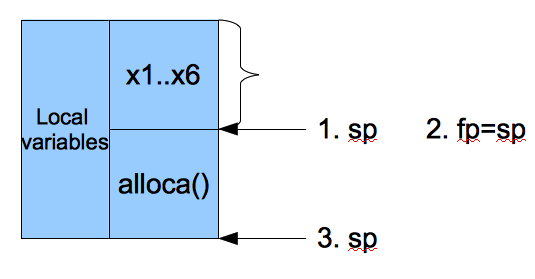

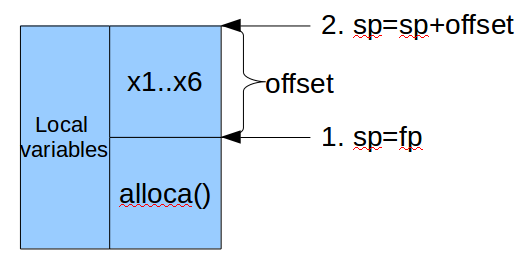

For the input ch9_incoming.cpp shown below, LowerFormalArguments() will

generate the red-boxed DAG nodes illustrated in Fig. 41

and Fig. 42, corresponding to

llc -cpu0-s32-calls=true and llc -cpu0-s32-calls=false, respectively.

The root node at the bottom is created by:

lbdex/input/ch9_incoming.cpp

int sum_i(int x1, int x2, int x3)

{

int sum = x1 + x2 + x3;

return sum;

}

JonathantekiiMac:input Jonathan$ clang -O3 -target mips-unknown-linux-gnu -c

ch9_incoming.cpp -emit-llvm -o ch9_incoming.bc

JonathantekiiMac:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llvm-dis ch9_incoming.bc -o -

...

define i32 @_Z5sum_iiii(i32 %x1, i32 %x2, i32 %x3) #0 {

%1 = add nsw i32 %x2, %x1

%2 = add nsw i32 %1, %x3

ret i32 %2

}

![digraph "dag-combine1 input for _Z5sum_iiii:" {

rankdir="BT";

// label="Incoming arguments DAG created for ch9_incoming.cpp with -cpu0-s32-calls=true";

subgraph cluster_0 {

fontcolor=red;

fontsize=24;

label = "LowerFormalArguments";

Node0x102f0dbe0 [shape=record,shape=Mrecord,label="{EntryToken|t0|{<d0>ch}}"];

Node0x10304e800 [shape=record,shape=Mrecord,label="{FrameIndex\<-1\>|t1|{<d0>i32}}"];

Node0x10304e870 [shape=record,shape=Mrecord,label="{undef|t2|{<d0>i32}}"];

Node0x10304e8e0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|load\<LD4[FixedStack-1]\>|t3|{<d0>i32|<d1>ch}}"];

Node0x10304e8e0:s0 -> Node0x102f0dbe0:d0[color=blue,style=dashed];

Node0x10304e8e0:s1 -> Node0x10304e800:d0;

Node0x10304e8e0:s2 -> Node0x10304e870:d0;

Node0x10304e950 [shape=record,shape=Mrecord,label="{FrameIndex\<-2\>|t4|{<d0>i32}}"];

Node0x10304e9c0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|load\<LD4[FixedStack-2]\>|t5|{<d0>i32|<d1>ch}}"];

Node0x10304e9c0:s0 -> Node0x102f0dbe0:d0[color=blue,style=dashed];

Node0x10304e9c0:s1 -> Node0x10304e950:d0;

Node0x10304e9c0:s2 -> Node0x10304e870:d0;

Node0x10304ea30 [shape=record,shape=Mrecord,label="{FrameIndex\<-3\>|t6|{<d0>i32}}"];

Node0x10304eaa0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|load\<LD4[FixedStack-3]\>|t7|{<d0>i32|<d1>ch}}"];

Node0x10304eaa0:s0 -> Node0x102f0dbe0:d0[color=blue,style=dashed];

Node0x10304eaa0:s1 -> Node0x10304ea30:d0;

Node0x10304eaa0:s2 -> Node0x10304e870:d0;

Node0x10304eb10 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2|<s3>3}|TokenFactor|t8|{<d0>ch}}"];

Node0x10304eb10:s0 -> Node0x10304e8e0:d1[color=blue,style=dashed];

Node0x10304eb10:s1 -> Node0x10304e9c0:d1[color=blue,style=dashed];

Node0x10304eb10:s2 -> Node0x10304eaa0:d1[color=blue,style=dashed];

Node0x10304eb10:s3 -> Node0x102f0dbe0:d0[color=blue,style=dashed];

Node0x10304eb80 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|add|t9|{<d0>i32}}"];

Node0x10304eb80:s0 -> Node0x10304e9c0:d0;

Node0x10304eb80:s1 -> Node0x10304e8e0:d0;

Node0x10304ebf0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|add|t10|{<d0>i32}}"];

Node0x10304ebf0:s0 -> Node0x10304eb80:d0;

Node0x10304ebf0:s1 -> Node0x10304eaa0:d0;

Node0x10304ec60 [shape=record,shape=Mrecord,label="{Register %V0|t11|{<d0>i32}}"];

}

subgraph cluster_1 {

fontcolor=red;

fontsize=24;

label = "LowerReturn";

Node0x10304ecd0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|CopyToReg|t12|{<d0>ch|<d1>glue}}"];

Node0x10304ecd0:s0 -> Node0x10304eb10:d0[color=blue,style=dashed];

Node0x10304ecd0:s1 -> Node0x10304ec60:d0;

Node0x10304ecd0:s2 -> Node0x10304ebf0:d0;

Node0x10304ed40 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|Cpu0ISD::Ret|t13|{<d0>ch}}"];

Node0x10304ed40:s0 -> Node0x10304ecd0:d0[color=blue,style=dashed];

Node0x10304ed40:s1 -> Node0x10304ec60:d0;

Node0x10304ed40:s2 -> Node0x10304ecd0:d1[color=red,style=bold];

}

Node0x0[ plaintext=circle, label ="GraphRoot"];

Node0x0 -> Node0x10304ed40:d0[color=blue,style=dashed];

}](_images/graphviz-b0110886547f51c2775ce9092a35be35d6cc7b17.png)

Fig. 41 Incoming arguments DAG created for ch9_incoming.cpp with -cpu0-s32-calls=true¶

![digraph "dag-combine1 input for _Z5sum_iiii:" {

rankdir="BT";

// label="Figure: Incoming arguments DAG created for ch9_incoming.cpp with -cpu0-s32-calls=false";

subgraph cluster_0 {

fontcolor=red;

fontsize=24;

label = "LowerFormalArguments";

Node0x102f0e0f0 [shape=record,shape=Mrecord,label="{EntryToken|t0|{<d0>ch}}"];

Node0x10305c200 [shape=record,shape=Mrecord,label="{Register %vreg0|t1|{<d0>i32}}"];

Node0x10305c270 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|CopyFromReg|t2|{<d0>i32|<d1>ch}}"];

Node0x10305c270:s0 -> Node0x102f0e0f0:d0[color=blue,style=dashed];

Node0x10305c270:s1 -> Node0x10305c200:d0;

Node0x10305c2e0 [shape=record,shape=Mrecord,label="{Register %vreg1|t3|{<d0>i32}}"];

Node0x10305c350 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|CopyFromReg|t4|{<d0>i32|<d1>ch}}"];

Node0x10305c350:s0 -> Node0x102f0e0f0:d0[color=blue,style=dashed];

Node0x10305c350:s1 -> Node0x10305c2e0:d0;

Node0x10305c3c0 [shape=record,shape=Mrecord,label="{FrameIndex\<-1\>|t5|{<d0>i32}}"];

Node0x10305c430 [shape=record,shape=Mrecord,label="{undef|t6|{<d0>i32}}"];

Node0x10305c4a0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|load\<LD4[FixedStack-1]\>|t7|{<d0>i32|<d1>ch}}"];

Node0x10305c4a0:s0 -> Node0x102f0e0f0:d0[color=blue,style=dashed];

Node0x10305c4a0:s1 -> Node0x10305c3c0:d0;

Node0x10305c4a0:s2 -> Node0x10305c430:d0;

Node0x10305c510 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|add|t8|{<d0>i32}}"];

Node0x10305c510:s0 -> Node0x10305c350:d0;

Node0x10305c510:s1 -> Node0x10305c270:d0;

Node0x10305c580 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|add|t9|{<d0>i32}}"];

Node0x10305c580:s0 -> Node0x10305c510:d0;

Node0x10305c580:s1 -> Node0x10305c4a0:d0;

Node0x10305c5f0 [shape=record,shape=Mrecord,label="{Register %V0|t10|{<d0>i32}}"];

}

subgraph cluster_1 {

fontcolor=red;

fontsize=24;

label = "LowerReturn";

Node0x10305c660 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|CopyToReg|t11|{<d0>ch|<d1>glue}}"];

Node0x10305c660:s0 -> Node0x10305c4a0:d1[color=blue,style=dashed];

Node0x10305c660:s1 -> Node0x10305c5f0:d0;

Node0x10305c660:s2 -> Node0x10305c580:d0;

Node0x10305c6d0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|Cpu0ISD::Ret|t12|{<d0>ch}}"];

Node0x10305c6d0:s0 -> Node0x10305c660:d0[color=blue,style=dashed];

Node0x10305c6d0:s1 -> Node0x10305c5f0:d0;

Node0x10305c6d0:s2 -> Node0x10305c660:d1[color=red,style=bold];

}

Node0x0[ plaintext=circle, label ="GraphRoot"];

Node0x0 -> Node0x10305c6d0:d0[color=blue,style=dashed];

}](_images/graphviz-5ed0ca5360e7d6c34af46f48366be7aa4a1c765c.png)

Fig. 42 Incoming arguments DAG created for ch9_incoming.cpp with -cpu0-s32-calls=false¶

In addition to the calling convention and LowerFormalArguments(), Chapter9_1/ adds support for instruction selection and printing of the Cpu0 instructions swi (software interrupt), jsub, and jalr (function call).

lbdex/chapters/Chapter9_1/Cpu0InstrInfo.td

def SDT_Cpu0JmpLink : SDTypeProfile<0, 1, [SDTCisVT<0, iPTR>]>;

// Call

def Cpu0JmpLink : SDNode<"Cpu0ISD::JmpLink",SDT_Cpu0JmpLink,

[SDNPHasChain, SDNPOutGlue, SDNPOptInGlue,

SDNPVariadic]>;

class IsTailCall {

bit isCall = 1;

bit isTerminator = 1;

bit isReturn = 1;

bit isBarrier = 1;

bit hasExtraSrcRegAllocReq = 1;

bit isCodeGenOnly = 1;

}

def calltarget : Operand<iPTR> {

let EncoderMethod = "getJumpTargetOpValue";

let OperandType = "OPERAND_PCREL";

}

let Predicates = [Ch9_1] in {

// Jump and Link (Call)

let isCall=1, hasDelaySlot=1 in {

//@JumpLink {

class JumpLink<bits<8> op, string instr_asm>:

FJ<op, (outs), (ins calltarget:$target, variable_ops),

!strconcat(instr_asm, "\t$target"), [(Cpu0JmpLink imm:$target)],

IIBranch> {

//#if CH >= CH10_1 2

let DecoderMethod = "DecodeJumpTarget";

//#endif

}

//@JumpLink }

class JumpLinkReg<bits<8> op, string instr_asm,

RegisterClass RC>:

FA<op, (outs), (ins RC:$rb, variable_ops),

!strconcat(instr_asm, "\t$rb"), [(Cpu0JmpLink RC:$rb)], IIBranch> {

let rc = 0;

let ra = 14;

let shamt = 0;

}

}

/// Jump & link and Return Instructions

let Predicates = [Ch9_1] in {

def JSUB : JumpLink<0x3b, "jsub">;

}

let Predicates = [Ch9_1] in {

def JALR : JumpLinkReg<0x39, "jalr", GPROut>;

}

let Predicates = [Ch9_1] in {

def : Pat<(Cpu0JmpLink (i32 tglobaladdr:$dst)),

(JSUB tglobaladdr:$dst)>;

def : Pat<(Cpu0JmpLink (i32 texternalsym:$dst)),

(JSUB texternalsym:$dst)>;

}

lbdex/chapters/Chapter9_1/Cpu0MCInstLower.cpp

MCOperand Cpu0MCInstLower::LowerSymbolOperand(const MachineOperand &MO,

MachineOperandType MOTy,

unsigned Offset) const {

MCSymbolRefExpr::VariantKind Kind = MCSymbolRefExpr::VK_None;

Cpu0MCExpr::Cpu0ExprKind TargetKind = Cpu0MCExpr::CEK_None;

const MCSymbol *Symbol;

switch(MO.getTargetFlags()) {

case Cpu0II::MO_GOT_CALL:

TargetKind = Cpu0MCExpr::CEK_GOT_CALL;

break;

...

}

switch (MOTy) {

. ...

case MachineOperand::MO_ExternalSymbol:

Symbol = AsmPrinter.GetExternalSymbolSymbol(MO.getSymbolName());

Offset += MO.getOffset();

break;

...

}

...

}

MCOperand Cpu0MCInstLower::LowerOperand(const MachineOperand& MO,

unsigned offset) const {

MachineOperandType MOTy = MO.getType();

switch (MOTy) {

//@2

case MachineOperand::MO_ExternalSymbol:

return LowerSymbolOperand(MO, MOTy, offset);

...

}

...

}

lbdex/chapters/Chapter9_1/MCTargetDesc/Cpu0AsmBackend.cpp

// Prepare value for the target space for it

static unsigned adjustFixupValue(const MCFixup &Fixup, uint64_t Value,

MCContext &Ctx) {

unsigned Kind = Fixup.getKind();

// Add/subtract and shift

switch (Kind) {

case Cpu0::fixup_Cpu0_CALL16:

...

}

...

}

lbdex/chapters/Chapter9_1/MCTargetDesc/Cpu0ELFObjectWriter.cpp

unsigned Cpu0ELFObjectWriter::getRelocType(MCContext &Ctx,

const MCValue &Target,

const MCFixup &Fixup,

bool IsPCRel) const {

// determine the type of the relocation

unsigned Type = (unsigned)ELF::R_CPU0_NONE;

unsigned Kind = (unsigned)Fixup.getKind();

switch (Kind) {

case Cpu0::fixup_Cpu0_CALL16:

Type = ELF::R_CPU0_CALL16;

break;

...

}

...

}

lbdex/chapters/Chapter9_1/MCTargetDesc/Cpu0FixupKinds.h

enum Fixups {

// resulting in - R_CPU0_CALL16.

fixup_Cpu0_CALL16,

...

. }

lbdex/chapters/Chapter9_1/MCTargetDesc/Cpu0MCCodeEmitter.cpp

unsigned Cpu0MCCodeEmitter::

getJumpTargetOpValue(const MCInst &MI, unsigned OpNo,

SmallVectorImpl<MCFixup> &Fixups,

const MCSubtargetInfo &STI) const {

if (Opcode == Cpu0::JSUB || Opcode == Cpu0::JMP || Opcode == Cpu0::BAL)

#elif CH >= CH8_2 //1

if (Opcode == Cpu0::JMP || Opcode == Cpu0::BAL)

Fixups.push_back(MCFixup::create(0, Expr,

MCFixupKind(Cpu0::fixup_Cpu0_PC24)));

...

}

unsigned Cpu0MCCodeEmitter::

getExprOpValue(const MCExpr *Expr,SmallVectorImpl<MCFixup> &Fixups,

const MCSubtargetInfo &STI) const {

// switch(cast<MCSymbolRefExpr>(Expr)->getKind()) {

case Cpu0MCExpr::CEK_GOT_CALL:

FixupKind = Cpu0::fixup_Cpu0_CALL16;

break;

...

}

...

}

lbdex/chapters/Chapter9_1/Cpu0MachineFunction.h

/// Cpu0FunctionInfo - This class is derived from MachineFunction private

/// Cpu0 target-specific information for each MachineFunction.

class Cpu0FunctionInfo : public MachineFunctionInfo {

public:

Cpu0FunctionInfo(MachineFunction& MF)

: MF(MF),

VarArgsFrameIndex(0),

InArgFIRange(std::make_pair(-1, 0)),

OutArgFIRange(std::make_pair(-1, 0)), GPFI(0), DynAllocFI(0),

bool isInArgFI(int FI) const {

return FI <= InArgFIRange.first && FI >= InArgFIRange.second;

}

void setLastInArgFI(int FI) { InArgFIRange.second = FI; }

bool isOutArgFI(int FI) const {

return FI <= OutArgFIRange.first && FI >= OutArgFIRange.second;

}

int getGPFI() const { return GPFI; }

void setGPFI(int FI) { GPFI = FI; }

bool isGPFI(int FI) const { return GPFI && GPFI == FI; }

bool isDynAllocFI(int FI) const { return DynAllocFI && DynAllocFI == FI; }

// Range of frame object indices.

// InArgFIRange: Range of indices of all frame objects created during call to

// LowerFormalArguments.

// OutArgFIRange: Range of indices of all frame objects created during call to

// LowerCall except for the frame object for restoring $gp.

std::pair<int, int> InArgFIRange, OutArgFIRange;

mutable int DynAllocFI; // Frame index of dynamically allocated stack area.

...

};

lbdex/chapters/Chapter9_1/Cpu0SEFrameLowering.h

bool spillCalleeSavedRegisters(MachineBasicBlock &MBB,

MachineBasicBlock::iterator MI,

ArrayRef<CalleeSavedInfo> CSI,

const TargetRegisterInfo *TRI) const override;

lbdex/chapters/Chapter9_1/Cpu0SEFrameLowering.cpp

bool Cpu0SEFrameLowering::

spillCalleeSavedRegisters(MachineBasicBlock &MBB,

MachineBasicBlock::iterator MI,

ArrayRef<CalleeSavedInfo> CSI,

const TargetRegisterInfo *TRI) const {

MachineFunction *MF = MBB.getParent();

MachineBasicBlock *EntryBlock = &MF->front();

const TargetInstrInfo &TII = *MF->getSubtarget().getInstrInfo();

for (unsigned i = 0, e = CSI.size(); i != e; ++i) {

// Add the callee-saved register as live-in. Do not add if the register is

// LR and return address is taken, because it has already been added in

// method Cpu0TargetLowering::LowerRETURNADDR.

// It's killed at the spill, unless the register is LR and return address

// is taken.

unsigned Reg = CSI[i].getReg();

bool IsRAAndRetAddrIsTaken = (Reg == Cpu0::LR)

&& MF->getFrameInfo().isReturnAddressTaken();

if (!IsRAAndRetAddrIsTaken)

EntryBlock->addLiveIn(Reg);

// Insert the spill to the stack frame.

bool IsKill = !IsRAAndRetAddrIsTaken;

const TargetRegisterClass *RC = TRI->getMinimalPhysRegClass(Reg);

TII.storeRegToStackSlot(*EntryBlock, MI, Reg, IsKill,

CSI[i].getFrameIdx(), RC, TRI);

}

return true;

}

Both JSUB and JALR, defined in Cpu0InstrInfo.td as shown above, use the Cpu0JmpLink node. They are distinguishable by their operand types: JSUB uses an imm (immediate) operand, while JALR uses a register operand.

lbdex/chapters/Chapter9_1/Cpu0InstrInfo.td

let Predicates = [Ch9_1] in {

def : Pat<(Cpu0JmpLink (i32 tglobaladdr:$dst)),

(JSUB tglobaladdr:$dst)>;

def : Pat<(Cpu0JmpLink (i32 texternalsym:$dst)),

(JSUB texternalsym:$dst)>;

The code instructs TableGen to generate pattern-matching logic that first matches the “imm” operand for the “tglobaladdr” pattern. If that match fails, it then attempts to match the “texternalsym” pattern.

A user-defined function belongs to the “tglobaladdr” category. For example, the function sum_i(…) defined in ch9_1.cpp falls under “tglobaladdr”.

On the other hand, functions implicitly used by LLVM, such as memcpy, belong to “texternalsym”. The memcpy function is typically generated when defining a long string. The file ch9_1_2.cpp is an example that triggers a call to memcpy. This will be shown in the next section with the Chapter9_2 example code.

The file Cpu0GenDAGISel.inc contains the pattern-matching information for JSUB and JALR, which is generated by TableGen as follows:

/*SwitchOpcode*/ 74, TARGET_VAL(Cpu0ISD::JmpLink),// ->734

/*660*/ OPC_RecordNode, // #0 = 'Cpu0JmpLink' chained node

/*661*/ OPC_CaptureGlueInput,

/*662*/ OPC_RecordChild1, // #1 = $target

/*663*/ OPC_Scope, 57, /*->722*/ // 2 children in Scope

/*665*/ OPC_MoveChild, 1,

/*667*/ OPC_SwitchOpcode /*3 cases */, 22, TARGET_VAL(ISD::Constant),

// ->693

/*671*/ OPC_MoveParent,

/*672*/ OPC_EmitMergeInputChains1_0,

/*673*/ OPC_EmitConvertToTarget, 1,

/*675*/ OPC_Scope, 7, /*->684*/ // 2 children in Scope

/*684*/ /*Scope*/ 7, /*->692*/

/*685*/ OPC_MorphNodeTo, TARGET_VAL(Cpu0::JSUB), 0|OPFL_Chain|

OPFL_GlueInput|OPFL_GlueOutput|OPFL_Variadic1,

0/*#VTs*/, 1/*#Ops*/, 2,

// Src: (Cpu0JmpLink (imm:iPTR):$target) - Complexity = 6

// Dst: (JSUB (imm:iPTR):$target)

/*692*/ 0, /*End of Scope*/

/*SwitchOpcode*/ 11, TARGET_VAL(ISD::TargetGlobalAddress),// ->707

/*696*/ OPC_CheckType, MVT::i32,

/*698*/ OPC_MoveParent,

/*699*/ OPC_EmitMergeInputChains1_0,

/*700*/ OPC_MorphNodeTo, TARGET_VAL(Cpu0::JSUB), 0|OPFL_Chain|

OPFL_GlueInput|OPFL_GlueOutput|OPFL_Variadic1,

0/*#VTs*/, 1/*#Ops*/, 1,

// Src: (Cpu0JmpLink (tglobaladdr:i32):$dst) - Complexity = 6

// Dst: (JSUB (tglobaladdr:i32):$dst)

/*SwitchOpcode*/ 11, TARGET_VAL(ISD::TargetExternalSymbol),// ->721

/*710*/ OPC_CheckType, MVT::i32,

/*712*/ OPC_MoveParent,

/*713*/ OPC_EmitMergeInputChains1_0,

/*714*/ OPC_MorphNodeTo, TARGET_VAL(Cpu0::JSUB), 0|OPFL_Chain|

OPFL_GlueInput|OPFL_GlueOutput|OPFL_Variadic1,

0/*#VTs*/, 1/*#Ops*/, 1,

// Src: (Cpu0JmpLink (texternalsym:i32):$dst) - Complexity = 6

// Dst: (JSUB (texternalsym:i32):$dst)

0, // EndSwitchOpcode

/*722*/ /*Scope*/ 10, /*->733*/

/*723*/ OPC_CheckChild1Type, MVT::i32,

/*725*/ OPC_EmitMergeInputChains1_0,

/*726*/ OPC_MorphNodeTo, TARGET_VAL(Cpu0::JALR), 0|OPFL_Chain|

OPFL_GlueInput|OPFL_GlueOutput|OPFL_Variadic1,

0/*#VTs*/, 1/*#Ops*/, 1,

// Src: (Cpu0JmpLink CPURegs:i32:$rb) - Complexity = 3

// Dst: (JALR CPURegs:i32:$rb)

/*733*/ 0, /*End of Scope*/

After applying the above changes, you can run Chapter9_1/ with ch9_1.cpp and observe the results as shown below:

118-165-79-83:input Jonathan$ /Users/Jonathan/llvm/test/

build/bin/llc -march=cpu0 -relocation-model=pic -filetype=asm

ch9_1.bc -o ch9_1.cpu0.s

Assertion failed: ((CLI.IsTailCall || InVals.size() == CLI.Ins.size()) &&

"LowerCall didn't emit the correct number of values!"), function LowerCallTo,

file /Users/Jonathan/llvm/test/llvm/lib/CodeGen/SelectionDAG/SelectionDAGBuilder.

cpp, ...

...

0. Program arguments: /Users/Jonathan/llvm/test/build/

bin/llc -march=cpu0 -relocation-model=pic -filetype=asm ch9_1.bc -o

ch9_1.cpu0.s

1. Running pass 'Function Pass Manager' on module 'ch9_1.bc'.

2. Running pass 'CPU0 DAG->DAG Pattern Instruction Selection' on function

'@main'

Illegal instruction: 4

Now, the LowerFormalArguments() has the correct number, but LowerCall() has not the correct number of values!

Store Outgoing Arguments to Stack Frame¶

Fig. 40 illustrates two steps involved in argument passing:

Storing outgoing arguments in the caller function.

Loading incoming arguments in the callee function.

In the previous section, we implemented LowerFormalArguments() to handle “loading incoming arguments” in the callee function.

Now, we will implement the part responsible for “storing outgoing arguments” in the caller function.

This task is handled by the LowerCall() function. Its implementation is shown below:

lbdex/chapters/Chapter9_2/Cpu0MachineFunction.h

/// Create a MachinePointerInfo that has an ExternalSymbolPseudoSourceValue

/// object representing a GOT entry for an external function.

MachinePointerInfo callPtrInfo(const char *ES);

/// Create a MachinePointerInfo that has a GlobalValuePseudoSourceValue object

/// representing a GOT entry for a global function.

MachinePointerInfo callPtrInfo(const GlobalValue *GV);

lbdex/chapters/Chapter9_2/Cpu0MachineFunction.cpp

MachinePointerInfo Cpu0FunctionInfo::callPtrInfo(const char *ES) {

return MachinePointerInfo(MF.getPSVManager().getExternalSymbolCallEntry(ES));

}

MachinePointerInfo Cpu0FunctionInfo::callPtrInfo(const GlobalValue *GV) {

return MachinePointerInfo(MF.getPSVManager().getGlobalValueCallEntry(GV));

}

lbdex/chapters/Chapter9_2/Cpu0ISelLowering.h

/// This function fills Ops, which is the list of operands that will later

/// be used when a function call node is created. It also generates

/// copyToReg nodes to set up argument registers.

virtual void

getOpndList(SmallVectorImpl<SDValue> &Ops,

std::deque< std::pair<unsigned, SDValue> > &RegsToPass,

bool IsPICCall, bool GlobalOrExternal, bool InternalLinkage,

CallLoweringInfo &CLI, SDValue Callee, SDValue Chain) const;

/// Cpu0CC - This class provides methods used to analyze formal and call

/// arguments and inquire about calling convention information.

class Cpu0CC {

void analyzeCallOperands(const SmallVectorImpl<ISD::OutputArg> &Outs,

bool IsVarArg, bool IsSoftFloat,

const SDNode *CallNode,

std::vector<ArgListEntry> &FuncArgs);

. };

Cpu0CC::SpecialCallingConvType getSpecialCallingConv(SDValue Callee) const;

// Lower Operand helpers

SDValue LowerCallResult(SDValue Chain, SDValue InFlag,

CallingConv::ID CallConv, bool isVarArg,

const SmallVectorImpl<ISD::InputArg> &Ins,

const SDLoc &dl, SelectionDAG &DAG,

SmallVectorImpl<SDValue> &InVals,

const SDNode *CallNode, const Type *RetTy) const;

/// passByValArg - Pass a byval argument in registers or on stack.

void passByValArg(SDValue Chain, const SDLoc &DL,

std::deque< std::pair<unsigned, SDValue> > &RegsToPass,

SmallVectorImpl<SDValue> &MemOpChains, SDValue StackPtr,

MachineFrameInfo &MFI, SelectionDAG &DAG, SDValue Arg,

const Cpu0CC &CC, const ByValArgInfo &ByVal,

const ISD::ArgFlagsTy &Flags, bool isLittle) const;

SDValue passArgOnStack(SDValue StackPtr, unsigned Offset, SDValue Chain,

SDValue Arg, const SDLoc &DL, bool IsTailCall,

SelectionDAG &DAG) const;

bool CanLowerReturn(CallingConv::ID CallConv, MachineFunction &MF,

bool isVarArg,

const SmallVectorImpl<ISD::OutputArg> &Outs,

LLVMContext &Context) const override;

lbdex/chapters/Chapter9_2/Cpu0ISelLowering.cpp

SDValue

Cpu0TargetLowering::passArgOnStack(SDValue StackPtr, unsigned Offset,

SDValue Chain, SDValue Arg, const SDLoc &DL,

bool IsTailCall, SelectionDAG &DAG) const {

if (!IsTailCall) {

SDValue PtrOff =

DAG.getNode(ISD::ADD, DL, getPointerTy(DAG.getDataLayout()), StackPtr,

DAG.getIntPtrConstant(Offset, DL));

return DAG.getStore(Chain, DL, Arg, PtrOff, MachinePointerInfo());

}

MachineFrameInfo &MFI = DAG.getMachineFunction().getFrameInfo();

int FI = MFI.CreateFixedObject(Arg.getValueSizeInBits() / 8, Offset, false);

SDValue FIN = DAG.getFrameIndex(FI, getPointerTy(DAG.getDataLayout()));

return DAG.getStore(Chain, DL, Arg, FIN, MachinePointerInfo(),

/* Alignment = */ 0, MachineMemOperand::MOVolatile);

}

void Cpu0TargetLowering::

getOpndList(SmallVectorImpl<SDValue> &Ops,

std::deque< std::pair<unsigned, SDValue> > &RegsToPass,

bool IsPICCall, bool GlobalOrExternal, bool InternalLinkage,

CallLoweringInfo &CLI, SDValue Callee, SDValue Chain) const {

// T9 should contain the address of the callee function if

// -reloction-model=pic or it is an indirect call.

if (IsPICCall || !GlobalOrExternal) {

unsigned T9Reg = Cpu0::T9;

RegsToPass.push_front(std::make_pair(T9Reg, Callee));

} else

Ops.push_back(Callee);

// Insert node "GP copy globalreg" before call to function.

//

// R_CPU0_CALL* operators (emitted when non-internal functions are called

// in PIC mode) allow symbols to be resolved via lazy binding.

// The lazy binding stub requires GP to point to the GOT.

if (IsPICCall && !InternalLinkage) {

unsigned GPReg = Cpu0::GP;

EVT Ty = MVT::i32;

RegsToPass.push_back(std::make_pair(GPReg, getGlobalReg(CLI.DAG, Ty)));

}

// Build a sequence of copy-to-reg nodes chained together with token

// chain and flag operands which copy the outgoing args into registers.

// The InFlag in necessary since all emitted instructions must be

// stuck together.

SDValue InFlag;

for (unsigned i = 0, e = RegsToPass.size(); i != e; ++i) {

Chain = CLI.DAG.getCopyToReg(Chain, CLI.DL, RegsToPass[i].first,

RegsToPass[i].second, InFlag);

InFlag = Chain.getValue(1);

}

// Add argument registers to the end of the list so that they are

// known live into the call.

for (unsigned i = 0, e = RegsToPass.size(); i != e; ++i)

Ops.push_back(CLI.DAG.getRegister(RegsToPass[i].first,

RegsToPass[i].second.getValueType()));

// Add a register mask operand representing the call-preserved registers.

const TargetRegisterInfo *TRI = Subtarget.getRegisterInfo();

const uint32_t *Mask =

TRI->getCallPreservedMask(CLI.DAG.getMachineFunction(), CLI.CallConv);

assert(Mask && "Missing call preserved mask for calling convention");

Ops.push_back(CLI.DAG.getRegisterMask(Mask));

if (InFlag.getNode())

Ops.push_back(InFlag);

}

/// LowerCall - functions arguments are copied from virtual regs to

/// (physical regs)/(stack frame), CALLSEQ_START and CALLSEQ_END are emitted.

SDValue

Cpu0TargetLowering::LowerCall(TargetLowering::CallLoweringInfo &CLI,

SmallVectorImpl<SDValue> &InVals) const {

SelectionDAG &DAG = CLI.DAG;

SDLoc DL = CLI.DL;

SmallVectorImpl<ISD::OutputArg> &Outs = CLI.Outs;

SmallVectorImpl<SDValue> &OutVals = CLI.OutVals;

SmallVectorImpl<ISD::InputArg> &Ins = CLI.Ins;

SDValue Chain = CLI.Chain;

SDValue Callee = CLI.Callee;

bool &IsTailCall = CLI.IsTailCall;

CallingConv::ID CallConv = CLI.CallConv;

bool IsVarArg = CLI.IsVarArg;

MachineFunction &MF = DAG.getMachineFunction();

MachineFrameInfo &MFI = MF.getFrameInfo();

const TargetFrameLowering *TFL = MF.getSubtarget().getFrameLowering();

Cpu0FunctionInfo *FuncInfo = MF.getInfo<Cpu0FunctionInfo>();

bool IsPIC = isPositionIndependent();

Cpu0FunctionInfo *Cpu0FI = MF.getInfo<Cpu0FunctionInfo>();

// Analyze operands of the call, assigning locations to each operand.

SmallVector<CCValAssign, 16> ArgLocs;

CCState CCInfo(CallConv, IsVarArg, DAG.getMachineFunction(),

ArgLocs, *DAG.getContext());

Cpu0CC::SpecialCallingConvType SpecialCallingConv =

getSpecialCallingConv(Callee);

Cpu0CC Cpu0CCInfo(CallConv, ABI.IsO32(),

CCInfo, SpecialCallingConv);

Cpu0CCInfo.analyzeCallOperands(Outs, IsVarArg,

Subtarget.abiUsesSoftFloat(),

Callee.getNode(), CLI.getArgs());

// Get a count of how many bytes are to be pushed on the stack.

unsigned NextStackOffset = CCInfo.getNextStackOffset();

//@TailCall 1 {

// Check if it's really possible to do a tail call.

if (IsTailCall)

IsTailCall =

isEligibleForTailCallOptimization(Cpu0CCInfo, NextStackOffset,

*MF.getInfo<Cpu0FunctionInfo>());

if (!IsTailCall && CLI.CB && CLI.CB->isMustTailCall())

report_fatal_error("failed to perform tail call elimination on a call "

"site marked musttail");

if (IsTailCall)

++NumTailCalls;

//@TailCall 1 }

// Chain is the output chain of the last Load/Store or CopyToReg node.

// ByValChain is the output chain of the last Memcpy node created for copying

// byval arguments to the stack.

unsigned StackAlignment = TFL->getStackAlignment();

NextStackOffset = alignTo(NextStackOffset, StackAlignment);

SDValue NextStackOffsetVal = DAG.getIntPtrConstant(NextStackOffset, DL, true);

//@TailCall 2 {

if (!IsTailCall)

Chain = DAG.getCALLSEQ_START(Chain, NextStackOffset, 0, DL);

//@TailCall 2 }

SDValue StackPtr =

DAG.getCopyFromReg(Chain, DL, Cpu0::SP,

getPointerTy(DAG.getDataLayout()));

// With EABI is it possible to have 16 args on registers.

std::deque< std::pair<unsigned, SDValue> > RegsToPass;

SmallVector<SDValue, 8> MemOpChains;

Cpu0CC::byval_iterator ByValArg = Cpu0CCInfo.byval_begin();

//@1 {

// Walk the register/memloc assignments, inserting copies/loads.

for (unsigned i = 0, e = ArgLocs.size(); i != e; ++i) {

//@1 }

SDValue Arg = OutVals[i];

CCValAssign &VA = ArgLocs[i];

MVT LocVT = VA.getLocVT();

ISD::ArgFlagsTy Flags = Outs[i].Flags;

//@ByVal Arg {

if (Flags.isByVal()) {

assert(Flags.getByValSize() &&

"ByVal args of size 0 should have been ignored by front-end.");

assert(ByValArg != Cpu0CCInfo.byval_end());

assert(!IsTailCall &&

"Do not tail-call optimize if there is a byval argument.");

passByValArg(Chain, DL, RegsToPass, MemOpChains, StackPtr, MFI, DAG, Arg,

Cpu0CCInfo, *ByValArg, Flags, Subtarget.isLittle());

++ByValArg;

continue;

}

//@ByVal Arg }

// Promote the value if needed.

switch (VA.getLocInfo()) {

default: llvm_unreachable("Unknown loc info!");

case CCValAssign::Full:

break;

case CCValAssign::SExt:

Arg = DAG.getNode(ISD::SIGN_EXTEND, DL, LocVT, Arg);

break;

case CCValAssign::ZExt:

Arg = DAG.getNode(ISD::ZERO_EXTEND, DL, LocVT, Arg);

break;

case CCValAssign::AExt:

Arg = DAG.getNode(ISD::ANY_EXTEND, DL, LocVT, Arg);

break;

}

// Arguments that can be passed on register must be kept at

// RegsToPass vector

if (VA.isRegLoc()) {

RegsToPass.push_back(std::make_pair(VA.getLocReg(), Arg));

continue;

}

// Register can't get to this point...

assert(VA.isMemLoc());

// emit ISD::STORE whichs stores the

// parameter value to a stack Location

MemOpChains.push_back(passArgOnStack(StackPtr, VA.getLocMemOffset(),

Chain, Arg, DL, IsTailCall, DAG));

}

// Transform all store nodes into one single node because all store

// nodes are independent of each other.

if (!MemOpChains.empty())

Chain = DAG.getNode(ISD::TokenFactor, DL, MVT::Other, MemOpChains);

// If the callee is a GlobalAddress/ExternalSymbol node (quite common, every

// direct call is) turn it into a TargetGlobalAddress/TargetExternalSymbol

// node so that legalize doesn't hack it.

bool IsPICCall = IsPIC; // true if calls are translated to

// jalr $t9

bool GlobalOrExternal = false, InternalLinkage = false;

EVT Ty = Callee.getValueType();

if (GlobalAddressSDNode *G = dyn_cast<GlobalAddressSDNode>(Callee)) {

if (IsPICCall) {

const GlobalValue *Val = G->getGlobal();

InternalLinkage = Val->hasInternalLinkage();

if (InternalLinkage)

Callee = getAddrLocal(G, Ty, DAG);

else

Callee = getAddrGlobal(G, Ty, DAG, Cpu0II::MO_GOT_CALL, Chain,

FuncInfo->callPtrInfo(Val));

} else

Callee = DAG.getTargetGlobalAddress(G->getGlobal(), DL,

getPointerTy(DAG.getDataLayout()), 0,

Cpu0II::MO_NO_FLAG);

GlobalOrExternal = true;

}

else if (ExternalSymbolSDNode *S = dyn_cast<ExternalSymbolSDNode>(Callee)) {

const char *Sym = S->getSymbol();

if (!IsPIC) // static

Callee = DAG.getTargetExternalSymbol(Sym,

getPointerTy(DAG.getDataLayout()),

Cpu0II::MO_NO_FLAG);

else // PIC

Callee = getAddrGlobal(S, Ty, DAG, Cpu0II::MO_GOT_CALL, Chain,

FuncInfo->callPtrInfo(Sym));

GlobalOrExternal = true;

}

SmallVector<SDValue, 8> Ops(1, Chain);

SDVTList NodeTys = DAG.getVTList(MVT::Other, MVT::Glue);

getOpndList(Ops, RegsToPass, IsPICCall, GlobalOrExternal, InternalLinkage,

CLI, Callee, Chain);

//@TailCall 3 {

if (IsTailCall)

return DAG.getNode(Cpu0ISD::TailCall, DL, MVT::Other, Ops);

//@TailCall 3 }

Chain = DAG.getNode(Cpu0ISD::JmpLink, DL, NodeTys, Ops);

SDValue InFlag = Chain.getValue(1);

// Create the CALLSEQ_END node.

Chain = DAG.getCALLSEQ_END(Chain, NextStackOffsetVal,

DAG.getIntPtrConstant(0, DL, true), InFlag, DL);

InFlag = Chain.getValue(1);

// Handle result values, copying them out of physregs into vregs that we

// return.

return LowerCallResult(Chain, InFlag, CallConv, IsVarArg,

Ins, DL, DAG, InVals, CLI.Callee.getNode(), CLI.RetTy);

}

/// LowerCallResult - Lower the result values of a call into the

/// appropriate copies out of appropriate physical registers.

SDValue

Cpu0TargetLowering::LowerCallResult(SDValue Chain, SDValue InFlag,

CallingConv::ID CallConv, bool IsVarArg,

const SmallVectorImpl<ISD::InputArg> &Ins,

const SDLoc &DL, SelectionDAG &DAG,

SmallVectorImpl<SDValue> &InVals,

const SDNode *CallNode,

const Type *RetTy) const {

// Assign locations to each value returned by this call.

SmallVector<CCValAssign, 16> RVLocs;

CCState CCInfo(CallConv, IsVarArg, DAG.getMachineFunction(),

RVLocs, *DAG.getContext());

Cpu0CC Cpu0CCInfo(CallConv, ABI.IsO32(), CCInfo);

Cpu0CCInfo.analyzeCallResult(Ins, Subtarget.abiUsesSoftFloat(),

CallNode, RetTy);

// Copy all of the result registers out of their specified physreg.

for (unsigned i = 0; i != RVLocs.size(); ++i) {

SDValue Val = DAG.getCopyFromReg(Chain, DL, RVLocs[i].getLocReg(),

RVLocs[i].getLocVT(), InFlag);

Chain = Val.getValue(1);

InFlag = Val.getValue(2);

if (RVLocs[i].getValVT() != RVLocs[i].getLocVT())

Val = DAG.getNode(ISD::BITCAST, DL, RVLocs[i].getValVT(), Val);

InVals.push_back(Val);

}

return Chain;

}

bool

Cpu0TargetLowering::CanLowerReturn(CallingConv::ID CallConv,

MachineFunction &MF, bool IsVarArg,

const SmallVectorImpl<ISD::OutputArg> &Outs,

LLVMContext &Context) const {

SmallVector<CCValAssign, 16> RVLocs;

CCState CCInfo(CallConv, IsVarArg, MF,

RVLocs, Context);

return CCInfo.CheckReturn(Outs, RetCC_Cpu0);

}

Cpu0TargetLowering::Cpu0CC::SpecialCallingConvType

Cpu0TargetLowering::getSpecialCallingConv(SDValue Callee) const {

Cpu0CC::SpecialCallingConvType SpecialCallingConv =

Cpu0CC::NoSpecialCallingConv;

return SpecialCallingConv;

}

void Cpu0TargetLowering::Cpu0CC::

analyzeCallOperands(const SmallVectorImpl<ISD::OutputArg> &Args,

bool IsVarArg, bool IsSoftFloat, const SDNode *CallNode,

std::vector<ArgListEntry> &FuncArgs) {

//@analyzeCallOperands body {

assert((CallConv != CallingConv::Fast || !IsVarArg) &&

"CallingConv::Fast shouldn't be used for vararg functions.");

unsigned NumOpnds = Args.size();

llvm::CCAssignFn *FixedFn = fixedArgFn();

//@3 {

for (unsigned I = 0; I != NumOpnds; ++I) {

//@3 }

MVT ArgVT = Args[I].VT;

ISD::ArgFlagsTy ArgFlags = Args[I].Flags;

bool R;

if (ArgFlags.isByVal()) {

handleByValArg(I, ArgVT, ArgVT, CCValAssign::Full, ArgFlags);

continue;

}

{

MVT RegVT = getRegVT(ArgVT, IsSoftFloat);

R = FixedFn(I, ArgVT, RegVT, CCValAssign::Full, ArgFlags, CCInfo);

}

if (R) {

#ifndef NDEBUG

dbgs() << "Call operand #" << I << " has unhandled type "

<< EVT(ArgVT).getEVTString();

#endif

llvm_unreachable(nullptr);

}

}

}

Just like loading incoming arguments from the stack frame, we call CCInfo(CallConv, …, ArgLocs, …) to obtain outgoing argument information before entering the “for loop”.

The loop structure is almost identical to that in LowerFormalArguments(), except that LowerCall() creates a “store DAG vector” instead of a “load DAG vector”.

After the “for loop”, it generates the instruction `ld $t9, %call16(_Z5sum_iiiiiii)($gp)` followed by jalr $t9 to call the subroutine (where $6 is $t9) in PIC (Position Independent Code) mode.

As with loading incoming arguments, we need to implement storeRegToStackSlot() in an earlier chapter to handle storing outgoing arguments.

Pseudo Hook Instructions ADJCALLSTACKDOWN and ADJCALLSTACKUP¶

DAG.getCALLSEQ_START() and DAG.getCALLSEQ_END() are invoked before and after the “for loop”, respectively. These insert CALLSEQ_START and CALLSEQ_END, which are later translated into the pseudo machine instructions ADJCALLSTACKDOWN and ADJCALLSTACKUP.

These pseudo instructions are defined in Cpu0InstrInfo.td as shown below:

lbdex/chapters/Chapter9_2/Cpu0InstrInfo.td

def SDT_Cpu0CallSeqStart : SDCallSeqStart<[SDTCisVT<0, i32>]>;

def SDT_Cpu0CallSeqEnd : SDCallSeqEnd<[SDTCisVT<0, i32>, SDTCisVT<1, i32>]>;

// These are target-independent nodes, but have target-specific formats.

def callseq_start : SDNode<"ISD::CALLSEQ_START", SDT_Cpu0CallSeqStart,

[SDNPHasChain, SDNPOutGlue]>;

def callseq_end : SDNode<"ISD::CALLSEQ_END", SDT_Cpu0CallSeqEnd,

[SDNPHasChain, SDNPOptInGlue, SDNPOutGlue]>;

//===----------------------------------------------------------------------===//

// Pseudo instructions

//===----------------------------------------------------------------------===//

let Predicates = [Ch9_2] in {

// As stack alignment is always done with addiu, we need a 16-bit immediate

let Defs = [SP], Uses = [SP] in {

def ADJCALLSTACKDOWN : Cpu0Pseudo<(outs), (ins uimm16:$amt1, uimm16:$amt2),

"!ADJCALLSTACKDOWN $amt1",

[(callseq_start timm:$amt1, timm:$amt2)]>;

def ADJCALLSTACKUP : Cpu0Pseudo<(outs), (ins uimm16:$amt1, uimm16:$amt2),

"!ADJCALLSTACKUP $amt1",

[(callseq_end timm:$amt1, timm:$amt2)]>;

}

//@def CPRESTORE {

// When handling PIC code the assembler needs .cpload and .cprestore

// directives. If the real instructions corresponding these directives

// are used, we have the same behavior, but get also a bunch of warnings

// from the assembler.

let hasSideEffects = 0 in

def CPRESTORE : Cpu0Pseudo<(outs), (ins i32imm:$loc, CPURegs:$gp),

".cprestore\t$loc", []>;

} // let Predicates = [Ch9_2]

With the definition below, eliminateCallFramePseudoInstr() will be called when LLVM encounters the pseudo instructions ADJCALLSTACKDOWN and ADJCALLSTACKUP.

This function simply discards these two pseudo instructions. LLVM will then automatically adjust the stack offset as needed.

lbdex/chapters/Chapter9_2/Cpu0InstrInfo.cpp

Cpu0InstrInfo::Cpu0InstrInfo(const Cpu0Subtarget &STI)

:

Cpu0GenInstrInfo(Cpu0::ADJCALLSTACKDOWN, Cpu0::ADJCALLSTACKUP),

lbdex/chapters/Chapter9_2/Cpu0FrameLowering.h

MachineBasicBlock::iterator

eliminateCallFramePseudoInstr(MachineFunction &MF,

MachineBasicBlock &MBB,

MachineBasicBlock::iterator I) const override;

lbdex/chapters/Chapter9_2/Cpu0FrameLowering.cpp

// Eliminate ADJCALLSTACKDOWN, ADJCALLSTACKUP pseudo instructions

MachineBasicBlock::iterator Cpu0FrameLowering::

eliminateCallFramePseudoInstr(MachineFunction &MF, MachineBasicBlock &MBB,

MachineBasicBlock::iterator I) const {

return MBB.erase(I);

}

Read LowerCall() with Graphviz’s Help¶

The complete DAGs created for outgoing arguments are shown in Fig. 43 for ch9_outgoing.cpp with cpu032I.

The LowerCall() function (excluding the call to LowerCallResult()) will generate the DAG nodes shown in Fig. 44 for ch9_outgoing.cpp with cpu032I.

The corresponding code for the DAG nodes Store and TargetGlobalAddress is listed in the figures. Users can match other DAG nodes to the LowerCall() function code accordingly.

By using the Graphviz tool with the llc option -view-dag-combine1-dags, you can design a small input in C or LLVM IR, then inspect the DAGs to better understand the behavior of LowerCall() and LowerFormalArguments().

In the later sub-sections, “Variable Arguments” and “Dynamic Stack Allocation Support”, you can create input examples that demonstrate these features. You can then use the DAGs to confirm your understanding of the logic in these two functions.

For more information about Graphviz, refer to the section “Display LLVM IR Nodes with Graphviz” in Chapter 4, Arithmetic and Logic Instructions.

The DAG diagrams can be generated using the llc option as shown below:

lbdex/input/ch9_outgoing.cpp

extern int sum_i(int x1);

int call_sum_i() {

return sum_i(1);

}

JonathantekiiMac:input Jonathan$ clang -O3 -target mips-unknown-linux-gnu -c

ch9_outgoing.cpp -emit-llvm -o ch9_outgoing.bc

JonathantekiiMac:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llvm-dis ch9_outgoing.bc -o -

...

define i32 @_Z10call_sum_iv() #0 {

%1 = tail call i32 @_Z5sum_ii(i32 1)

ret i32 %1

}

JonathantekiiMac:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llc -march=cpu0 -mcpu=cpu032I -view-dag-combine1-dags -relocation-

model=static -filetype=asm ch9_outgoing.bc -o -

.text

.section .mdebug.abiS32

.previous

.file "ch9_outgoing.bc"

Writing '/var/folders/rf/8bgdgt9d6vgf5sn8h8_zycd00000gn/T/dag._Z10call_sum_iv-

0dfaf1.dot'... done.

Running 'Graphviz' program...

![digraph "dag-combine1 input for _Z10call_sum_iv:" {

rankdir="BT";

// label="Figure Outgoing arguments DAG (A) created for ch9_outgoing.cpp with -cpu0-s32-calls=true";

subgraph cluster_0 {

fontcolor=red;

fontsize=24;

label = "LowerCall";

Node0x102f0d060 [shape=record,shape=Mrecord,label="{EntryToken|t0|{<d0>ch}}"];

Node0x10304f200 [shape=record,shape=Mrecord,label="{GlobalAddress\<i32 (i32)* @_Z5sum_ii\> 0|t1|{<d0>i32}}"];

Node0x10304f270 [shape=record,shape=Mrecord,label="{Constant\<1\>|t2|{<d0>i32}}"];

Node0x10304f2e0 [shape=record,shape=Mrecord,label="{TargetConstant\<8\>|t3|{<d0>i32}}"];

Node0x10304f350 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|callseq_start|t4|{<d0>ch|<d1>glue}}"];

Node0x10304f350:s0 -> Node0x102f0d060:d0[color=blue,style=dashed];

Node0x10304f350:s1 -> Node0x10304f2e0:d0;

Node0x10304f3c0 [shape=record,shape=Mrecord,label="{Register %SP|t5|{<d0>i32}}"];

Node0x10304f430 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|CopyFromReg|t6|{<d0>i32|<d1>ch}}"];

Node0x10304f430:s0 -> Node0x10304f350:d0[color=blue,style=dashed];

Node0x10304f430:s1 -> Node0x10304f3c0:d0;

Node0x10304f4a0 [shape=record,shape=Mrecord,label="{Constant\<0\>|t7|{<d0>i32}}"];

Node0x10304f510 [shape=record,shape=Mrecord,label="{undef|t8|{<d0>i32}}"];

Node0x10304f580 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2|<s3>3}|store\<ST4[\<unknown\>]\>|t9|{<d0>ch}}"];

Node0x10304f580:s0 -> Node0x10304f350:d0[color=blue,style=dashed];

Node0x10304f580:s1 -> Node0x10304f270:d0;

Node0x10304f580:s2 -> Node0x10304f430:d0;

Node0x10304f580:s3 -> Node0x10304f510:d0;

Node0x10304f5f0 [shape=record,shape=Mrecord,label="{TargetGlobalAddress\<i32 (i32)* @_Z5sum_ii\> 0|t10|{<d0>i32}}"];

Node0x10304f660 [shape=record,shape=Mrecord,label="{RegisterMask|t11|{<d0>Untyped}}"];

Node0x10304f6d0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|Cpu0ISD::JmpLink|t12|{<d0>ch|<d1>glue}}"];

Node0x10304f6d0:s0 -> Node0x10304f580:d0[color=blue,style=dashed];

Node0x10304f6d0:s1 -> Node0x10304f5f0:d0;

Node0x10304f6d0:s2 -> Node0x10304f660:d0;

Node0x10304f740 [shape=record,shape=Mrecord,label="{TargetConstant\<0\>|t13|{<d0>i32}}"];

Node0x10304f7b0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2|<s3>3}|callseq_end|t14|{<d0>ch|<d1>glue}}"];

Node0x10304f7b0:s0 -> Node0x10304f6d0:d0[color=blue,style=dashed];

Node0x10304f7b0:s1 -> Node0x10304f2e0:d0;

Node0x10304f7b0:s2 -> Node0x10304f740:d0;

Node0x10304f7b0:s3 -> Node0x10304f6d0:d1[color=red,style=bold];

}

subgraph cluster_1 {

fontcolor=red;

fontsize=24;

label = "LowerCallResult";

Node0x10304f820 [shape=record,shape=Mrecord,label="{Register %V0|t15|{<d0>i32}}"];

Node0x10304f890 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|CopyFromReg|t16|{<d0>i32|<d1>ch|<d2>glue}}"];

}

subgraph cluster_2 {

fontcolor=red;

fontsize=24;

label = "LowerReturn";

Node0x10304f900 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|CopyToReg|t17|{<d0>ch|<d1>glue}}"];

Node0x10304f970 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|Cpu0ISD::Ret|t18|{<d0>ch}}"];

}

Node0x10304f890:s0 -> Node0x10304f7b0:d0[color=blue,style=dashed];

Node0x10304f890:s1 -> Node0x10304f820:d0;

Node0x10304f890:s2 -> Node0x10304f7b0:d1[color=red,style=bold];

Node0x10304f900:s0 -> Node0x10304f890:d1[color=blue,style=dashed];

Node0x10304f900:s1 -> Node0x10304f820:d0;

Node0x10304f900:s2 -> Node0x10304f890:d0;

Node0x10304f970:s0 -> Node0x10304f900:d0[color=blue,style=dashed];

Node0x10304f970:s1 -> Node0x10304f820:d0;

Node0x10304f970:s2 -> Node0x10304f900:d1[color=red,style=bold];

Node0x0[ plaintext=circle, label ="GraphRoot"];

Node0x0 -> Node0x10304f970:d0[color=blue,style=dashed];

}](_images/graphviz-2ff535f052608d39fd4598743c0a09315e673459.png)

Fig. 43 Outgoing arguments DAG (A) created for ch9_outgoing.cpp with -cpu0-s32-calls=true¶

![digraph "isel input for _Z10call_sum_iv:" {

rankdir="BT";

// label="Figure Outgoing arguments DAG (B) created by LowerCall() for ch9_outgoing.cpp with -cpu0-s32-calls=true";

Node0x102f0d060 [shape=record,shape=Mrecord,label="{EntryToken|t0|{<d0>ch}}"];

Node0x10304f270 [shape=record,shape=Mrecord,label="{Constant\<1\>|t2|{<d0>i32}}"];

Node0x10304f2e0 [shape=record,shape=Mrecord,label="{TargetConstant\<8\>|t3|{<d0>i32}}"];

Node0x10304f350 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|callseq_start|t4|{<d0>ch|<d1>glue}}"];

Node0x10304f350:s0 -> Node0x102f0d060:d0[color=blue,style=dashed];

Node0x10304f350:s1 -> Node0x10304f2e0:d0;

Node0x10304f3c0 [shape=record,shape=Mrecord,label="{Register %SP|t5|{<d0>i32}}"];

Node0x10304f430 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1}|CopyFromReg|t6|{<d0>i32|<d1>ch}}"];

Node0x10304f430:s0 -> Node0x10304f350:d0[color=blue,style=dashed];

Node0x10304f430:s1 -> Node0x10304f3c0:d0;

Node0x10304f510 [shape=record,shape=Mrecord,label="{undef|t8|{<d0>i32}}"];

Node0x10304f580 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2|<s3>3}|store\<ST4[\<unknown\>]\>|t9|{<d0>ch}}"];

Node0x10304f580:s0 -> Node0x10304f350:d0[color=blue,style=dashed];

Node0x10304f580:s1 -> Node0x10304f270:d0;

Node0x10304f580:s2 -> Node0x10304f430:d0;

Node0x10304f580:s3 -> Node0x10304f510:d0;

Node0x10304f5f0 [shape=record,shape=Mrecord,label="{TargetGlobalAddress\<i32 (i32)* @_Z5sum_ii\> 0|t10|{<d0>i32}}"];

Node0x10304f660 [shape=record,shape=Mrecord,label="{RegisterMask|t11|{<d0>Untyped}}"];

Node0x10304f6d0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2}|Cpu0ISD::JmpLink|t12|{<d0>ch|<d1>glue}}"];

Node0x10304f6d0:s0 -> Node0x10304f580:d0[color=blue,style=dashed];

Node0x10304f6d0:s1 -> Node0x10304f5f0:d0;

Node0x10304f6d0:s2 -> Node0x10304f660:d0;

Node0x10304f740 [shape=record,shape=Mrecord,label="{TargetConstant\<0\>|t13|{<d0>i32}}"];

Node0x10304f7b0 [shape=record,shape=Mrecord,label="{{<s0>0|<s1>1|<s2>2|<s3>3}|callseq_end|t14|{<d0>ch|<d1>glue}}"];

Node0x10304f7b0:s0 -> Node0x10304f6d0:d0[color=blue,style=dashed];

Node0x10304f7b0:s1 -> Node0x10304f2e0:d0;

Node0x10304f7b0:s2 -> Node0x10304f740:d0;

Node0x10304f7b0:s3 -> Node0x10304f6d0:d1[color=red,style=bold];

NodeComment1 [ penwidth = 1, fontname = "Courier New", shape = "note", label =<<table border="0" cellborder="0" cellpadding="3" bgcolor="gray">

<tr><td align="left">// Transform all store nodes into one single node because all store</td></tr>

<tr><td align="left" port="f1">// nodes are independent of each other.</td></tr>

<tr><td align="left" port="f2">if (!MemOpChains.empty())</td></tr>

<tr><td align="left" port="f3"> Chain = DAG.getNode(ISD::TokenFactor, DL, MVT::Other, MemOpChains);</td></tr>

<tr><td align="left"> ...</td></tr>

</table>> ];

NodeComment2 [ penwidth = 1, fontname = "Courier New", shape = "note", label =<<table border="0" cellborder="0" cellpadding="3" bgcolor="gray">

<tr><td align="left">if (!IsPIC) // static</td></tr>

<tr><td align="left" port="f1"> Callee = DAG.getTargetExternalSymbol(Sym,</td></tr>

<tr><td align="left" port="f2"> getPointerTy(DAG.getDataLayout()),</td></tr>

<tr><td align="left" port="f3"> Cpu0II::MO_NO_FLAG);</td></tr>

<tr><td align="left"> ...</td></tr>

</table>> ];

Node0x10304f580 -> NodeComment1[color=black,style=dashed];

NodeComment2:n -> Node0x10304f6d0:e[color=black,style=dashed];

}](_images/graphviz-1278f18ff1ad05a8af2e93b2e3df50121888a5df.png)

Fig. 44 Outgoing arguments DAG (B) created by LowerCall() for ch9_outgoing.cpp with -cpu0-s32-calls=true¶

As mentioned in the previous section, the option llc -cpu0-s32-calls=true

uses the S32 calling convention, which passes all arguments in registers.

In contrast, the option llc -cpu0-s32-calls=false uses the O32 convention,

which passes the first two arguments in registers and the remaining arguments

on the stack.

The resulting behavior is shown as follows:

118-165-78-230:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llc -march=cpu0 -mcpu=cpu032I -cpu0-s32-calls=true

-relocation-model=pic -filetype=asm ch9_1.bc -o -

.text

.section .mdebug.abiS32

.previous

.file "ch9_1.bc"

.globl _Z5sum_iiiiiii

.align 2

.type _Z5sum_iiiiiii,@function

.ent _Z5sum_iiiiiii # @_Z5sum_iiiiiii

_Z5sum_iiiiiii:

.frame $fp,32,$lr

.mask 0x00000000,0

.set noreorder

.cpload $t9

.set nomacro

# BB#0:

addiu $sp, $sp, -32

ld $2, 52($sp)

ld $3, 48($sp)

ld $4, 44($sp)

ld $5, 40($sp)

ld $t9, 36($sp)

ld $7, 32($sp)

st $7, 28($sp)

st $t9, 24($sp)

st $5, 20($sp)

st $4, 16($sp)

st $3, 12($sp)

lui $3, %got_hi(gI)

addu $3, $3, $gp

st $2, 8($sp)

ld $3, %got_lo(gI)($3)

ld $3, 0($3)

ld $4, 28($sp)

addu $3, $3, $4

ld $4, 24($sp)

addu $3, $3, $4

ld $4, 20($sp)

addu $3, $3, $4

ld $4, 16($sp)

addu $3, $3, $4

ld $4, 12($sp)

addu $3, $3, $4

addu $2, $3, $2

st $2, 4($sp)

addiu $sp, $sp, 32

ret $lr

nop

.set macro

.set reorder

.end _Z5sum_iiiiiii

$tmp0:

.size _Z5sum_iiiiiii, ($tmp0)-_Z5sum_iiiiiii

.globl main

.align 2

.type main,@function

.ent main # @main

main:

.frame $fp,40,$lr

.mask 0x00004000,-4

.set noreorder

.cpload $t9

.set nomacro

# BB#0:

addiu $sp, $sp, -40

st $lr, 36($sp) # 4-byte Folded Spill

addiu $2, $zero, 0

st $2, 32($sp)

addiu $2, $zero, 6

st $2, 20($sp)

addiu $2, $zero, 5

st $2, 16($sp)

addiu $2, $zero, 4

st $2, 12($sp)

addiu $2, $zero, 3

st $2, 8($sp)

addiu $2, $zero, 2

st $2, 4($sp)

addiu $2, $zero, 1

st $2, 0($sp)

ld $t9, %call16(_Z5sum_iiiiiii)($gp)

jalr $t9

nop

st $2, 28($sp)

ld $lr, 36($sp) # 4-byte Folded Reload

addiu $sp, $sp, 40

ret $lr

nop

.set macro

.set reorder

.end main

$tmp1:

.size main, ($tmp1)-main

.type gI,@object # @gI

.data

.globl gI

.align 2

gI:

.4byte 100 # 0x64

.size gI, 4

118-165-78-230:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llc -march=cpu0 -mcpu=cpu032II -cpu0-s32-calls=false

-relocation-model=pic -filetype=asm ch9_1.bc -o -

...

.globl main

.align 2

.type main,@function

.ent main # @main

main:

.frame $fp,40,$lr

.mask 0x00004000,-4

.set noreorder

.cpload $t9

.set nomacro

# BB#0:

addiu $sp, $sp, -40

st $lr, 36($sp) # 4-byte Folded Spill

addiu $2, $zero, 0

st $2, 32($sp)

addiu $2, $zero, 6

st $2, 20($sp)

addiu $2, $zero, 5

st $2, 16($sp)

addiu $2, $zero, 4

st $2, 12($sp)

addiu $2, $zero, 3

st $2, 8($sp)

ld $t9, %call16(_Z5sum_iiiiiii)($gp)

addiu $4, $zero, 1

addiu $5, $zero, 2

jalr $t9

nop

st $2, 28($sp)