Backend structure¶

From Fig. 11, llvm compiler transfer from llvm-ir to assembly or binary object with the following data structure as Fig. 16.

Fig. 16 LLVM data structure used in different stages¶

Cpu0 backend supports the following backend compiler, assembler and disassembler as Fig. 17, Fig. 18 and Fig. 19. However only the green part for printing assembly is implemented in this chapter. Others are implemented in later chapters Fig. 31, Fig. 55 and Fig. 50.

![digraph G {

rankdir=LR;

subgraph clusterDisa {

label = "Disassembler";

objdump [label="llvm-objdump", shape=record];

obj_dis [label="binary obj"];

asm_dis [label="assembly"];

obj_dis -> objdump;

objdump -> asm_dis [label="-d"];

}

subgraph clusterAsm {

label = "Assembler";

llc_asm [label="llc", shape=record];

asm_asm [label="assembly"];

obj_asm [label="binary obj"];

asm_asm -> llc_asm;

llc_asm -> obj_asm [label="-filetype=obj"];

}

subgraph clusterLlc {

label = "Backend compiler";

llc_llc [label="llc", shape=record];

asm_llc [label="assembly"];

obj_llc [label="binary obj"];

"llvm-ir" -> llc_llc;

llc_llc -> asm_llc [label="-filetype=asm"];

llc_llc -> obj_llc [label="-filetype=obj"];

}

}](_images/graphviz-a869858052b9b9e5de29795804e821090add87a3.png)

Fig. 17 Backend compiler, assembler and disassembler of Cpu0¶

![digraph G {

rankdir=LR;

"MCInst" -> "assembly" [label="printInst()"];

"MCInst" -> "binary object" [label="emitInstruction()"];

"assembly" -> "MCInst" [label="MatchAndEmitInstruction()"];

"binary object" -> "MCInst" [label="getInstruction()"];

}](_images/graphviz-1f74d88c9c587bf3b33dda6c4f158714db318cb6.png)

Fig. 18 Encode, assembler and disassembler¶

![digraph G {

rankdir=TB;

llc [label="llc", shape=record];

llvm_objdump [label="llvm-objdump", shape=record];

asm_file [label="asm file", shape=record];

bin_file [labe="binary file", shape=record];

llc -> EI_Asm [label="[input-file=llvm-ir]\nMachineInstr"];

EI_Asm -> "printInst()" [label="MCInst"];

EI_Asm -> EI_MC [label="MCInst"];

"printInst()" -> asm_file;

EI_MC -> bin_file;

llc -> "MatchAndEmitInstruction()" [label="[input-file=asm]\nOpcode,Operands"];

"MatchAndEmitInstruction()" -> EI_MC [label="MCInst"];

llvm_objdump -> "getInstruction()" [label="[input-file=binary]\nBytes"];

llvm_objdump -> "printInst()" [label="MCInst"];

subgraph clusterCpu0Asm {

label = "Cpu0AsmPrinter.cpp";

EI_Asm [label="emitInstruction()", style="filled,bold", fillcolor="lightgreen"];

}

subgraph clusterCpu0InstPrinter {

label = "Cpu0InstPrinter.cpp\nCpu0GenAsmWrite.inc(from Cpu0InstrInfo.td)";

"printInst()" [style="filled,bold", fillcolor="lightgreen"];

}

subgraph clusterCpu0MC {

label = "Cpu0MCCodeEmitter.cpp\nCpu0GenMCCodeEmitter.inc(from Cpu0InstrInfo.td)";

EI_MC [label="emitInstruction()"];

}

subgraph clusterCpu0AsmParser {

label = "Cpu0AsmParser.cpp\nCpu0GenAsmMatcher.inc(from Cpu0InstrInfo.td)";

"MatchAndEmitInstruction()";

}

subgraph clusterCpu0Dis {

label = "Cpu0Disassembler.cpp\nCpu0GenDisassemblerTables.inc(from Cpu0InstrInfo.td)";

"getInstruction()";

}

}](_images/graphviz-b359f207b814de3c237849742106c7b79e37f4ab.png)

Fig. 19 The structure for backend compiler, assembler and disassembler of Cpu0¶

Bytes: 4-byte (32-bits) for Cpu0.

Each MInst contains one single instruction.

The encoder extracts information from MachineInstr and places it into MCInst. It then calls printInst() to generate assembly instructions or emitInstruction() to output binary instruction.

The assembler calls MatchAndEmitInstruction() to convert assembly back into MCInst, then calls emitInstruction() to output binary instruction.

The disassembler calls getInstruction() to convert binary instructions back into MCInst, then calls printInst() to generate assembly instruction.

The emitInstruction() of Cpu0MCCodeEmitter.cpp: encode binary for an instruction reused for both llc (compiler) and llc (assembler).

The printInst() of Cpu0InstPrinter.cpp: print assembly code for an instruction reused for both llc (compiler) and llvm-objdump (disassembler).

This chapter first introduces the backend class inheritance tree and its class members. Then, following the backend structure, we add individual class implementations in each section. By the end of this chapter, we will have a backend capable of compiling LLVM intermediate code into Cpu0 assembly code.

Many lines of code are introduced in this chapter. Most of them are common across different backends, except for the backend name (e.g., Cpu0 or Mips). In fact, we copy almost all the code from Mips and replace the name with Cpu0. Beyond understanding DAG pattern matching in theoretical compilers and the LLVM code generation phase, please focus on the relationships between classes in this backend structure. Once you grasp the structure, you will be able to create your backend as quickly as we did, even though this chapter introduces around 5000 lines of code.

TargetMachine structure¶

lbdex/chapters/Chapter3_1/Cpu0TargetObjectFile.h

//===-- llvm/Target/Cpu0TargetObjectFile.h - Cpu0 Object Info ---*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0TARGETOBJECTFILE_H

#define LLVM_LIB_TARGET_CPU0_CPU0TARGETOBJECTFILE_H

#include "Cpu0Config.h"

#include "Cpu0TargetMachine.h"

#include "llvm/CodeGen/TargetLoweringObjectFileImpl.h"

namespace llvm {

class Cpu0TargetMachine;

class Cpu0TargetObjectFile : public TargetLoweringObjectFileELF {

MCSection *SmallDataSection;

MCSection *SmallBSSSection;

const Cpu0TargetMachine *TM;

public:

void Initialize(MCContext &Ctx, const TargetMachine &TM) override;

};

} // end namespace llvm

#endif

lbdex/chapters/Chapter3_1/Cpu0TargetObjectFile.cpp

//===-- Cpu0TargetObjectFile.cpp - Cpu0 Object Files ----------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

#include "Cpu0TargetObjectFile.h"

#include "Cpu0Subtarget.h"

#include "Cpu0TargetMachine.h"

#include "llvm/BinaryFormat/ELF.h"

#include "llvm/IR/DataLayout.h"

#include "llvm/IR/DerivedTypes.h"

#include "llvm/IR/GlobalVariable.h"

#include "llvm/MC/MCContext.h"

#include "llvm/MC/MCSectionELF.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Target/TargetMachine.h"

using namespace llvm;

static cl::opt<unsigned>

SSThreshold("cpu0-ssection-threshold", cl::Hidden,

cl::desc("Small data and bss section threshold size (default=8)"),

cl::init(8));

void Cpu0TargetObjectFile::Initialize(MCContext &Ctx, const TargetMachine &TM){

TargetLoweringObjectFileELF::Initialize(Ctx, TM);

InitializeELF(TM.Options.UseInitArray);

SmallDataSection = getContext().getELFSection(

".sdata", ELF::SHT_PROGBITS, ELF::SHF_WRITE | ELF::SHF_ALLOC);

SmallBSSSection = getContext().getELFSection(".sbss", ELF::SHT_NOBITS,

ELF::SHF_WRITE | ELF::SHF_ALLOC);

this->TM = &static_cast<const Cpu0TargetMachine &>(TM);

}

lbdex/chapters/Chapter3_1/Cpu0TargetMachine.h

//===-- Cpu0TargetMachine.h - Define TargetMachine for Cpu0 -----*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file declares the Cpu0 specific subclass of TargetMachine.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0TARGETMACHINE_H

#define LLVM_LIB_TARGET_CPU0_CPU0TARGETMACHINE_H

#include "Cpu0Config.h"

#include "MCTargetDesc/Cpu0ABIInfo.h"

#include "Cpu0Subtarget.h"

#include "llvm/CodeGen/Passes.h"

#include "llvm/CodeGen/SelectionDAGISel.h"

#include "llvm/CodeGen/TargetFrameLowering.h"

#include "llvm/Support/CodeGen.h"

#include "llvm/Target/TargetMachine.h"

namespace llvm {

class formatted_raw_ostream;

class Cpu0RegisterInfo;

class Cpu0TargetMachine : public LLVMTargetMachine {

bool isLittle;

std::unique_ptr<TargetLoweringObjectFile> TLOF;

// Selected ABI

Cpu0ABIInfo ABI;

Cpu0Subtarget DefaultSubtarget;

mutable StringMap<std::unique_ptr<Cpu0Subtarget>> SubtargetMap;

public:

Cpu0TargetMachine(const Target &T, const Triple &TT, StringRef CPU,

StringRef FS, const TargetOptions &Options,

Optional<Reloc::Model> RM, Optional<CodeModel::Model> CM,

CodeGenOpt::Level OL, bool JIT, bool isLittle);

~Cpu0TargetMachine() override;

const Cpu0Subtarget *getSubtargetImpl() const {

return &DefaultSubtarget;

}

const Cpu0Subtarget *getSubtargetImpl(const Function &F) const override;

// Pass Pipeline Configuration

TargetPassConfig *createPassConfig(PassManagerBase &PM) override;

TargetLoweringObjectFile *getObjFileLowering() const override {

return TLOF.get();

}

bool isLittleEndian() const { return isLittle; }

const Cpu0ABIInfo &getABI() const { return ABI; }

};

/// Cpu0ebTargetMachine - Cpu032 big endian target machine.

///

class Cpu0ebTargetMachine : public Cpu0TargetMachine {

virtual void anchor();

public:

Cpu0ebTargetMachine(const Target &T, const Triple &TT, StringRef CPU,

StringRef FS, const TargetOptions &Options,

Optional<Reloc::Model> RM, Optional<CodeModel::Model> CM,

CodeGenOpt::Level OL, bool JIT);

};

/// Cpu0elTargetMachine - Cpu032 little endian target machine.

///

class Cpu0elTargetMachine : public Cpu0TargetMachine {

virtual void anchor();

public:

Cpu0elTargetMachine(const Target &T, const Triple &TT, StringRef CPU,

StringRef FS, const TargetOptions &Options,

Optional<Reloc::Model> RM, Optional<CodeModel::Model> CM,

CodeGenOpt::Level OL, bool JIT);

};

} // End llvm namespace

#endif

lbdex/chapters/Chapter3_1/Cpu0TargetMachine.cpp

//===-- Cpu0TargetMachine.cpp - Define TargetMachine for Cpu0 -------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// Implements the info about Cpu0 target spec.

//

//===----------------------------------------------------------------------===//

#include "Cpu0TargetMachine.h"

#include "Cpu0.h"

#include "Cpu0Subtarget.h"

#include "Cpu0TargetObjectFile.h"

#include "llvm/IR/Attributes.h"

#include "llvm/IR/Function.h"

#include "llvm/Support/CodeGen.h"

#include "llvm/CodeGen/Passes.h"

#include "llvm/CodeGen/TargetPassConfig.h"

#include "llvm/Support/TargetRegistry.h"

#include "llvm/Target/TargetOptions.h"

using namespace llvm;

#define DEBUG_TYPE "cpu0"

extern "C" void LLVMInitializeCpu0Target() {

// Register the target.

//- Big endian Target Machine

RegisterTargetMachine<Cpu0ebTargetMachine> X(TheCpu0Target);

//- Little endian Target Machine

RegisterTargetMachine<Cpu0elTargetMachine> Y(TheCpu0elTarget);

}

static std::string computeDataLayout(const Triple &TT, StringRef CPU,

const TargetOptions &Options,

bool isLittle) {

std::string Ret = "";

// There are both little and big endian cpu0.

if (isLittle)

Ret += "e";

else

Ret += "E";

Ret += "-m:m";

// Pointers are 32 bit on some ABIs.

Ret += "-p:32:32";

// 8 and 16 bit integers only need to have natural alignment, but try to

// align them to 32 bits. 64 bit integers have natural alignment.

Ret += "-i8:8:32-i16:16:32-i64:64";

// 32 bit registers are always available and the stack is at least 64 bit

// aligned.

Ret += "-n32-S64";

return Ret;

}

static Reloc::Model getEffectiveRelocModel(bool JIT,

Optional<Reloc::Model> RM) {

if (!RM.hasValue() || JIT)

return Reloc::Static;

return *RM;

}

// DataLayout --> Big-endian, 32-bit pointer/ABI/alignment

// The stack is always 8 byte aligned

// On function prologue, the stack is created by decrementing

// its pointer. Once decremented, all references are done with positive

// offset from the stack/frame pointer, using StackGrowsUp enables

// an easier handling.

// Using CodeModel::Large enables different CALL behavior.

Cpu0TargetMachine::Cpu0TargetMachine(const Target &T, const Triple &TT,

StringRef CPU, StringRef FS,

const TargetOptions &Options,

Optional<Reloc::Model> RM,

Optional<CodeModel::Model> CM,

CodeGenOpt::Level OL, bool JIT,

bool isLittle)

//- Default is big endian

: LLVMTargetMachine(T, computeDataLayout(TT, CPU, Options, isLittle), TT,

CPU, FS, Options, getEffectiveRelocModel(JIT, RM),

getEffectiveCodeModel(CM, CodeModel::Small), OL),

isLittle(isLittle), TLOF(std::make_unique<Cpu0TargetObjectFile>()),

ABI(Cpu0ABIInfo::computeTargetABI()),

DefaultSubtarget(TT, CPU, FS, isLittle, *this) {

// initAsmInfo will display features by llc -march=cpu0 -mcpu=help on 3.7 but

// not on 3.6

initAsmInfo();

}

Cpu0TargetMachine::~Cpu0TargetMachine() {}

void Cpu0ebTargetMachine::anchor() { }

Cpu0ebTargetMachine::Cpu0ebTargetMachine(const Target &T, const Triple &TT,

StringRef CPU, StringRef FS,

const TargetOptions &Options,

Optional<Reloc::Model> RM,

Optional<CodeModel::Model> CM,

CodeGenOpt::Level OL, bool JIT)

: Cpu0TargetMachine(T, TT, CPU, FS, Options, RM, CM, OL, JIT, false) {}

void Cpu0elTargetMachine::anchor() { }

Cpu0elTargetMachine::Cpu0elTargetMachine(const Target &T, const Triple &TT,

StringRef CPU, StringRef FS,

const TargetOptions &Options,

Optional<Reloc::Model> RM,

Optional<CodeModel::Model> CM,

CodeGenOpt::Level OL, bool JIT)

: Cpu0TargetMachine(T, TT, CPU, FS, Options, RM, CM, OL, JIT, true) {}

const Cpu0Subtarget *

Cpu0TargetMachine::getSubtargetImpl(const Function &F) const {

std::string CPU = TargetCPU;

std::string FS = TargetFS;

auto &I = SubtargetMap[CPU + FS];

if (!I) {

// This needs to be done before we create a new subtarget since any

// creation will depend on the TM and the code generation flags on the

// function that reside in TargetOptions.

resetTargetOptions(F);

I = std::make_unique<Cpu0Subtarget>(TargetTriple, CPU, FS, isLittle,

*this);

}

return I.get();

}

namespace {

//@Cpu0PassConfig {

/// Cpu0 Code Generator Pass Configuration Options.

class Cpu0PassConfig : public TargetPassConfig {

public:

Cpu0PassConfig(Cpu0TargetMachine &TM, PassManagerBase &PM)

: TargetPassConfig(TM, PM) {}

Cpu0TargetMachine &getCpu0TargetMachine() const {

return getTM<Cpu0TargetMachine>();

}

const Cpu0Subtarget &getCpu0Subtarget() const {

return *getCpu0TargetMachine().getSubtargetImpl();

}

};

} // namespace

TargetPassConfig *Cpu0TargetMachine::createPassConfig(PassManagerBase &PM) {

return new Cpu0PassConfig(*this, PM);

}

include/llvm/Target/TargetInstInfo.h

class TargetInstrInfo : public MCInstrInfo {

TargetInstrInfo(const TargetInstrInfo &) = delete;

void operator=(const TargetInstrInfo &) = delete;

public:

...

}

...

class TargetInstrInfoImpl : public TargetInstrInfo {

protected:

TargetInstrInfoImpl(int CallFrameSetupOpcode = -1,

int CallFrameDestroyOpcode = -1)

: TargetInstrInfo(CallFrameSetupOpcode, CallFrameDestroyOpcode) {}

public:

...

}

lbdex/chapters/Chapter3_1/Cpu0.td

include "Cpu0CallingConv.td"

lbdex/chapters/Chapter3_1/Cpu0CallingConv.td

//===-- Cpu0CallingConv.td - Calling Conventions for Cpu0 --*- tablegen -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

// This describes the calling conventions for Cpu0 architecture.

//===----------------------------------------------------------------------===//

/// CCIfSubtarget - Match if the current subtarget has a feature F.

class CCIfSubtarget<string F, CCAction A>:

CCIf<!strconcat("State.getTarget().getSubtarget<Cpu0Subtarget>().", F), A>;

def CSR_O32 : CalleeSavedRegs<(add LR, FP,

(sequence "S%u", 1, 0))>;

lbdex/chapters/Chapter3_1/Cpu0FrameLowering.h

//===-- Cpu0FrameLowering.h - Define frame lowering for Cpu0 ----*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

//

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0FRAMELOWERING_H

#define LLVM_LIB_TARGET_CPU0_CPU0FRAMELOWERING_H

#include "Cpu0Config.h"

#include "Cpu0.h"

#include "llvm/CodeGen/TargetFrameLowering.h"

namespace llvm {

class Cpu0Subtarget;

class Cpu0FrameLowering : public TargetFrameLowering {

protected:

const Cpu0Subtarget &STI;

public:

explicit Cpu0FrameLowering(const Cpu0Subtarget &sti, unsigned Alignment)

: TargetFrameLowering(StackGrowsDown, Align(Alignment), 0, Align(Alignment)),

STI(sti) {

}

static const Cpu0FrameLowering *create(const Cpu0Subtarget &ST);

bool hasFP(const MachineFunction &MF) const override;

};

/// Create Cpu0FrameLowering objects.

const Cpu0FrameLowering *createCpu0SEFrameLowering(const Cpu0Subtarget &ST);

} // End llvm namespace

#endif

lbdex/chapters/Chapter3_1/Cpu0FrameLowering.cpp

//===-- Cpu0FrameLowering.cpp - Cpu0 Frame Information --------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the Cpu0 implementation of TargetFrameLowering class.

//

//===----------------------------------------------------------------------===//

#include "Cpu0FrameLowering.h"

#include "Cpu0InstrInfo.h"

#include "Cpu0MachineFunction.h"

#include "Cpu0Subtarget.h"

#include "llvm/CodeGen/MachineFrameInfo.h"

#include "llvm/CodeGen/MachineFunction.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/CodeGen/MachineModuleInfo.h"

#include "llvm/CodeGen/MachineRegisterInfo.h"

#include "llvm/IR/DataLayout.h"

#include "llvm/IR/Function.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Target/TargetOptions.h"

using namespace llvm;

//- emitPrologue() and emitEpilogue must exist for main().

//===----------------------------------------------------------------------===//

//

// Stack Frame Processing methods

// +----------------------------+

//

// The stack is allocated decrementing the stack pointer on

// the first instruction of a function prologue. Once decremented,

// all stack references are done thought a positive offset

// from the stack/frame pointer, so the stack is considering

// to grow up! Otherwise terrible hacks would have to be made

// to get this stack ABI compliant :)

//

// The stack frame required by the ABI (after call):

// Offset

//

// 0 ----------

// 4 Args to pass

// . saved $GP (used in PIC)

// . Alloca allocations

// . Local Area

// . CPU "Callee Saved" Registers

// . saved FP

// . saved RA

// . FPU "Callee Saved" Registers

// StackSize -----------

//

// Offset - offset from sp after stack allocation on function prologue

//

// The sp is the stack pointer subtracted/added from the stack size

// at the Prologue/Epilogue

//

// References to the previous stack (to obtain arguments) are done

// with offsets that exceeds the stack size: (stacksize+(4*(num_arg-1))

//

// Examples:

// - reference to the actual stack frame

// for any local area var there is smt like : FI >= 0, StackOffset: 4

// st REGX, 4(SP)

//

// - reference to previous stack frame

// suppose there's a load to the 5th arguments : FI < 0, StackOffset: 16.

// The emitted instruction will be something like:

// ld REGX, 16+StackSize(SP)

//

// Since the total stack size is unknown on LowerFormalArguments, all

// stack references (ObjectOffset) created to reference the function

// arguments, are negative numbers. This way, on eliminateFrameIndex it's

// possible to detect those references and the offsets are adjusted to

// their real location.

//

//===----------------------------------------------------------------------===//

const Cpu0FrameLowering *Cpu0FrameLowering::create(const Cpu0Subtarget &ST) {

return llvm::createCpu0SEFrameLowering(ST);

}

// hasFP - Return true if the specified function should have a dedicated frame

// pointer register. This is true if the function has variable sized allocas,

// if it needs dynamic stack realignment, if frame pointer elimination is

// disabled, or if the frame address is taken.

bool Cpu0FrameLowering::hasFP(const MachineFunction &MF) const {

const MachineFrameInfo &MFI = MF.getFrameInfo();

const TargetRegisterInfo *TRI = STI.getRegisterInfo();

return MF.getTarget().Options.DisableFramePointerElim(MF) ||

MFI.hasVarSizedObjects() || MFI.isFrameAddressTaken() ||

TRI->needsStackRealignment(MF);

}

lbdex/chapters/Chapter3_1/Cpu0SEFrameLowering.h

//===-- Cpu0SEFrameLowering.h - Cpu032/64 frame lowering --------*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

//

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0SEFRAMELOWERING_H

#define LLVM_LIB_TARGET_CPU0_CPU0SEFRAMELOWERING_H

#include "Cpu0Config.h"

#include "Cpu0FrameLowering.h"

namespace llvm {

class Cpu0SEFrameLowering : public Cpu0FrameLowering {

public:

explicit Cpu0SEFrameLowering(const Cpu0Subtarget &STI);

/// emitProlog/emitEpilog - These methods insert prolog and epilog code into

/// the function.

void emitPrologue(MachineFunction &MF, MachineBasicBlock &MBB) const override;

void emitEpilogue(MachineFunction &MF, MachineBasicBlock &MBB) const override;

};

} // End llvm namespace

#endif

lbdex/chapters/Chapter3_1/Cpu0SEFrameLowering.cpp

//===-- Cpu0SEFrameLowering.cpp - Cpu0 Frame Information ------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the Cpu0 implementation of TargetFrameLowering class.

//

//===----------------------------------------------------------------------===//

#include "Cpu0SEFrameLowering.h"

#include "Cpu0MachineFunction.h"

#include "Cpu0SEInstrInfo.h"

#include "Cpu0Subtarget.h"

#include "llvm/CodeGen/MachineFrameInfo.h"

#include "llvm/CodeGen/MachineFunction.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/CodeGen/MachineModuleInfo.h"

#include "llvm/CodeGen/MachineRegisterInfo.h"

#include "llvm/CodeGen/RegisterScavenging.h"

#include "llvm/IR/DataLayout.h"

#include "llvm/IR/Function.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Target/TargetOptions.h"

using namespace llvm;

Cpu0SEFrameLowering::Cpu0SEFrameLowering(const Cpu0Subtarget &STI)

: Cpu0FrameLowering(STI, STI.stackAlignment()) {}

//@emitPrologue {

void Cpu0SEFrameLowering::emitPrologue(MachineFunction &MF,

MachineBasicBlock &MBB) const {

}

//}

//@emitEpilogue {

void Cpu0SEFrameLowering::emitEpilogue(MachineFunction &MF,

MachineBasicBlock &MBB) const {

}

//}

const Cpu0FrameLowering *

llvm::createCpu0SEFrameLowering(const Cpu0Subtarget &ST) {

return new Cpu0SEFrameLowering(ST);

}

lbdex/chapters/Chapter3_1/Cpu0InstrInfo.h

//===-- Cpu0InstrInfo.h - Cpu0 Instruction Information ----------*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the Cpu0 implementation of the TargetInstrInfo class.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0INSTRINFO_H

#define LLVM_LIB_TARGET_CPU0_CPU0INSTRINFO_H

#include "Cpu0Config.h"

#include "Cpu0.h"

#include "Cpu0RegisterInfo.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/CodeGen/TargetInstrInfo.h"

#define GET_INSTRINFO_HEADER

#include "Cpu0GenInstrInfo.inc"

namespace llvm {

class Cpu0InstrInfo : public Cpu0GenInstrInfo {

virtual void anchor();

protected:

const Cpu0Subtarget &Subtarget;

public:

explicit Cpu0InstrInfo(const Cpu0Subtarget &STI);

static const Cpu0InstrInfo *create(Cpu0Subtarget &STI);

/// getRegisterInfo - TargetInstrInfo is a superset of MRegister info. As

/// such, whenever a client has an instance of instruction info, it should

/// always be able to get register info as well (through this method).

///

virtual const Cpu0RegisterInfo &getRegisterInfo() const = 0;

/// Return the number of bytes of code the specified instruction may be.

unsigned GetInstSizeInBytes(const MachineInstr &MI) const;

protected:

};

const Cpu0InstrInfo *createCpu0SEInstrInfo(const Cpu0Subtarget &STI);

}

#endif

lbdex/chapters/Chapter3_1/Cpu0InstrInfo.cpp

//===-- Cpu0InstrInfo.cpp - Cpu0 Instruction Information ------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the Cpu0 implementation of the TargetInstrInfo class.

//

//===----------------------------------------------------------------------===//

#include "Cpu0InstrInfo.h"

#include "Cpu0TargetMachine.h"

#include "Cpu0MachineFunction.h"

#include "llvm/ADT/STLExtras.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/Support/ErrorHandling.h"

#include "llvm/Support/TargetRegistry.h"

using namespace llvm;

#define GET_INSTRINFO_CTOR_DTOR

#include "Cpu0GenInstrInfo.inc"

// Pin the vtable to this file.

void Cpu0InstrInfo::anchor() {}

//@Cpu0InstrInfo {

Cpu0InstrInfo::Cpu0InstrInfo(const Cpu0Subtarget &STI)

:

Subtarget(STI) {}

const Cpu0InstrInfo *Cpu0InstrInfo::create(Cpu0Subtarget &STI) {

return llvm::createCpu0SEInstrInfo(STI);

}

//@GetInstSizeInBytes {

/// Return the number of bytes of code the specified instruction may be.

unsigned Cpu0InstrInfo::GetInstSizeInBytes(const MachineInstr &MI) const {

//@GetInstSizeInBytes - body

switch (MI.getOpcode()) {

default:

return MI.getDesc().getSize();

}

}

lbdex/chapters/Chapter3_1/Cpu0InstrInfo.td

//===----------------------------------------------------------------------===//

// Cpu0 Instruction Predicate Definitions.

//===----------------------------------------------------------------------===//

def Ch3_1 : Predicate<"Subtarget->hasChapter3_1()">,

AssemblerPredicate<(all_of FeatureChapter3_1)>;

def Ch3_2 : Predicate<"Subtarget->hasChapter3_2()">,

AssemblerPredicate<(all_of FeatureChapter3_2)>;

def Ch3_3 : Predicate<"Subtarget->hasChapter3_3()">,

AssemblerPredicate<(all_of FeatureChapter3_3)>;

def Ch3_4 : Predicate<"Subtarget->hasChapter3_4()">,

AssemblerPredicate<(all_of FeatureChapter3_4)>;

def Ch3_5 : Predicate<"Subtarget->hasChapter3_5()">,

AssemblerPredicate<(all_of FeatureChapter3_5)>;

def Ch4_1 : Predicate<"Subtarget->hasChapter4_1()">,

AssemblerPredicate<(all_of FeatureChapter4_1)>;

def Ch4_2 : Predicate<"Subtarget->hasChapter4_2()">,

AssemblerPredicate<(all_of FeatureChapter4_2)>;

def Ch5_1 : Predicate<"Subtarget->hasChapter5_1()">,

AssemblerPredicate<(all_of FeatureChapter5_1)>;

def Ch6_1 : Predicate<"Subtarget->hasChapter6_1()">,

AssemblerPredicate<(all_of FeatureChapter6_1)>;

def Ch7_1 : Predicate<"Subtarget->hasChapter7_1()">,

AssemblerPredicate<(all_of FeatureChapter7_1)>;

def Ch8_1 : Predicate<"Subtarget->hasChapter8_1()">,

AssemblerPredicate<(all_of FeatureChapter8_1)>;

def Ch8_2 : Predicate<"Subtarget->hasChapter8_2()">,

AssemblerPredicate<(all_of FeatureChapter8_2)>;

def Ch9_1 : Predicate<"Subtarget->hasChapter9_1()">,

AssemblerPredicate<(all_of FeatureChapter9_1)>;

def Ch9_2 : Predicate<"Subtarget->hasChapter9_2()">,

AssemblerPredicate<(all_of FeatureChapter9_2)>;

def Ch9_3 : Predicate<"Subtarget->hasChapter9_3()">,

AssemblerPredicate<(all_of FeatureChapter9_3)>;

def Ch10_1 : Predicate<"Subtarget->hasChapter10_1()">,

AssemblerPredicate<(all_of FeatureChapter10_1)>;

def Ch11_1 : Predicate<"Subtarget->hasChapter11_1()">,

AssemblerPredicate<(all_of FeatureChapter11_1)>;

def Ch11_2 : Predicate<"Subtarget->hasChapter11_2()">,

AssemblerPredicate<(all_of FeatureChapter11_2)>;

def Ch12_1 : Predicate<"Subtarget->hasChapter12_1()">,

AssemblerPredicate<(all_of FeatureChapter12_1)>;

def Ch_all : Predicate<"Subtarget->hasChapterAll()">,

AssemblerPredicate<(all_of FeatureChapterAll)>;

def EnableOverflow : Predicate<"Subtarget->enableOverflow()">;

def DisableOverflow : Predicate<"Subtarget->disableOverflow()">;

def HasCmp : Predicate<"Subtarget->hasCmp()">;

def HasSlt : Predicate<"Subtarget->hasSlt()">;

lbdex/chapters/Chapter3_1/Cpu0ISelLowering.h

//===-- Cpu0ISelLowering.h - Cpu0 DAG Lowering Interface --------*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file defines the interfaces that Cpu0 uses to lower LLVM code into a

// selection DAG.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0ISELLOWERING_H

#define LLVM_LIB_TARGET_CPU0_CPU0ISELLOWERING_H

#include "Cpu0Config.h"

#include "MCTargetDesc/Cpu0ABIInfo.h"

#include "Cpu0.h"

#include "llvm/CodeGen/CallingConvLower.h"

#include "llvm/CodeGen/SelectionDAG.h"

#include "llvm/IR/Function.h"

#include "llvm/CodeGen/TargetLowering.h"

#include <deque>

namespace llvm {

namespace Cpu0ISD {

enum NodeType {

// Start the numbering from where ISD NodeType finishes.

FIRST_NUMBER = ISD::BUILTIN_OP_END,

// Jump and link (call)

JmpLink,

// Tail call

TailCall,

// Get the Higher 16 bits from a 32-bit immediate

// No relation with Cpu0 Hi register

Hi,

// Get the Lower 16 bits from a 32-bit immediate

// No relation with Cpu0 Lo register

Lo,

// Handle gp_rel (small data/bss sections) relocation.

GPRel,

// Thread Pointer

ThreadPointer,

// Return

Ret,

EH_RETURN,

// DivRem(u)

DivRem,

DivRemU,

Wrapper,

DynAlloc,

Sync

};

}

//===--------------------------------------------------------------------===//

// TargetLowering Implementation

//===--------------------------------------------------------------------===//

class Cpu0FunctionInfo;

class Cpu0Subtarget;

//@class Cpu0TargetLowering

class Cpu0TargetLowering : public TargetLowering {

public:

explicit Cpu0TargetLowering(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI);

static const Cpu0TargetLowering *create(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI);

/// getTargetNodeName - This method returns the name of a target specific

// DAG node.

const char *getTargetNodeName(unsigned Opcode) const override;

protected:

/// ByValArgInfo - Byval argument information.

struct ByValArgInfo {

unsigned FirstIdx; // Index of the first register used.

unsigned NumRegs; // Number of registers used for this argument.

unsigned Address; // Offset of the stack area used to pass this argument.

ByValArgInfo() : FirstIdx(0), NumRegs(0), Address(0) {}

};

protected:

// Subtarget Info

const Cpu0Subtarget &Subtarget;

// Cache the ABI from the TargetMachine, we use it everywhere.

const Cpu0ABIInfo &ABI;

private:

// Lower Operand specifics

SDValue lowerGlobalAddress(SDValue Op, SelectionDAG &DAG) const;

//- must be exist even without function all

SDValue

LowerFormalArguments(SDValue Chain,

CallingConv::ID CallConv, bool IsVarArg,

const SmallVectorImpl<ISD::InputArg> &Ins,

const SDLoc &dl, SelectionDAG &DAG,

SmallVectorImpl<SDValue> &InVals) const override;

SDValue LowerReturn(SDValue Chain,

CallingConv::ID CallConv, bool IsVarArg,

const SmallVectorImpl<ISD::OutputArg> &Outs,

const SmallVectorImpl<SDValue> &OutVals,

const SDLoc &dl, SelectionDAG &DAG) const override;

};

const Cpu0TargetLowering *

createCpu0SETargetLowering(const Cpu0TargetMachine &TM, const Cpu0Subtarget &STI);

}

#endif // Cpu0ISELLOWERING_H

lbdex/chapters/Chapter3_1/Cpu0ISelLowering.cpp

//===-- Cpu0ISelLowering.cpp - Cpu0 DAG Lowering Implementation -----------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file defines the interfaces that Cpu0 uses to lower LLVM code into a

// selection DAG.

//

//===----------------------------------------------------------------------===//

#include "Cpu0ISelLowering.h"

#include "Cpu0MachineFunction.h"

#include "Cpu0TargetMachine.h"

#include "Cpu0TargetObjectFile.h"

#include "Cpu0Subtarget.h"

#include "llvm/ADT/Statistic.h"

#include "llvm/CodeGen/CallingConvLower.h"

#include "llvm/CodeGen/MachineFrameInfo.h"

#include "llvm/CodeGen/MachineFunction.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/CodeGen/MachineRegisterInfo.h"

#include "llvm/CodeGen/SelectionDAG.h"

#include "llvm/CodeGen/ValueTypes.h"

#include "llvm/IR/CallingConv.h"

#include "llvm/IR/DerivedTypes.h"

#include "llvm/IR/GlobalVariable.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Support/Debug.h"

#include "llvm/Support/ErrorHandling.h"

#include "llvm/Support/raw_ostream.h"

using namespace llvm;

#define DEBUG_TYPE "cpu0-lower"

//@3_1 1 {

const char *Cpu0TargetLowering::getTargetNodeName(unsigned Opcode) const {

switch (Opcode) {

case Cpu0ISD::JmpLink: return "Cpu0ISD::JmpLink";

case Cpu0ISD::TailCall: return "Cpu0ISD::TailCall";

case Cpu0ISD::Hi: return "Cpu0ISD::Hi";

case Cpu0ISD::Lo: return "Cpu0ISD::Lo";

case Cpu0ISD::GPRel: return "Cpu0ISD::GPRel";

case Cpu0ISD::Ret: return "Cpu0ISD::Ret";

case Cpu0ISD::EH_RETURN: return "Cpu0ISD::EH_RETURN";

case Cpu0ISD::DivRem: return "Cpu0ISD::DivRem";

case Cpu0ISD::DivRemU: return "Cpu0ISD::DivRemU";

case Cpu0ISD::Wrapper: return "Cpu0ISD::Wrapper";

default: return NULL;

}

}

//@3_1 1 }

//@Cpu0TargetLowering {

Cpu0TargetLowering::Cpu0TargetLowering(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI)

: TargetLowering(TM), Subtarget(STI), ABI(TM.getABI()) {

}

const Cpu0TargetLowering *Cpu0TargetLowering::create(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI) {

return llvm::createCpu0SETargetLowering(TM, STI);

}

//===----------------------------------------------------------------------===//

// Lower helper functions

//===----------------------------------------------------------------------===//

//===----------------------------------------------------------------------===//

// Misc Lower Operation implementation

//===----------------------------------------------------------------------===//

#include "Cpu0GenCallingConv.inc"

//===----------------------------------------------------------------------===//

//@ Formal Arguments Calling Convention Implementation

//===----------------------------------------------------------------------===//

//@LowerFormalArguments {

/// LowerFormalArguments - transform physical registers into virtual registers

/// and generate load operations for arguments places on the stack.

SDValue

Cpu0TargetLowering::LowerFormalArguments(SDValue Chain,

CallingConv::ID CallConv,

bool IsVarArg,

const SmallVectorImpl<ISD::InputArg> &Ins,

const SDLoc &DL, SelectionDAG &DAG,

SmallVectorImpl<SDValue> &InVals)

const {

return Chain;

}

// @LowerFormalArguments }

//===----------------------------------------------------------------------===//

//@ Return Value Calling Convention Implementation

//===----------------------------------------------------------------------===//

SDValue

Cpu0TargetLowering::LowerReturn(SDValue Chain,

CallingConv::ID CallConv, bool IsVarArg,

const SmallVectorImpl<ISD::OutputArg> &Outs,

const SmallVectorImpl<SDValue> &OutVals,

const SDLoc &DL, SelectionDAG &DAG) const {

return DAG.getNode(Cpu0ISD::Ret, DL, MVT::Other,

Chain, DAG.getRegister(Cpu0::LR, MVT::i32));

}

lbdex/chapters/Chapter3_1/Cpu0SEISelLowering.h

//===-- Cpu0ISEISelLowering.h - Cpu0ISE DAG Lowering Interface ----*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// Subclass of Cpu0ITargetLowering specialized for cpu032/64.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0SEISELLOWERING_H

#define LLVM_LIB_TARGET_CPU0_CPU0SEISELLOWERING_H

#include "Cpu0Config.h"

#include "Cpu0ISelLowering.h"

#include "Cpu0RegisterInfo.h"

namespace llvm {

class Cpu0SETargetLowering : public Cpu0TargetLowering {

public:

explicit Cpu0SETargetLowering(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI);

SDValue LowerOperation(SDValue Op, SelectionDAG &DAG) const override;

private:

};

}

#endif // Cpu0ISEISELLOWERING_H

lbdex/chapters/Chapter3_1/Cpu0SEISelLowering.cpp

//===-- Cpu0SEISelLowering.cpp - Cpu0SE DAG Lowering Interface --*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// Subclass of Cpu0TargetLowering specialized for cpu032.

//

//===----------------------------------------------------------------------===//

#include "Cpu0MachineFunction.h"

#include "Cpu0SEISelLowering.h"

#include "Cpu0RegisterInfo.h"

#include "Cpu0TargetMachine.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/CodeGen/MachineRegisterInfo.h"

#include "llvm/CodeGen/TargetInstrInfo.h"

#include "llvm/IR/Intrinsics.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Support/Debug.h"

#include "llvm/Support/raw_ostream.h"

using namespace llvm;

#define DEBUG_TYPE "cpu0-isel"

static cl::opt<bool>

EnableCpu0TailCalls("enable-cpu0-tail-calls", cl::Hidden,

cl::desc("CPU0: Enable tail calls."), cl::init(false));

//@Cpu0SETargetLowering {

Cpu0SETargetLowering::Cpu0SETargetLowering(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI)

: Cpu0TargetLowering(TM, STI) {

//@Cpu0SETargetLowering body {

// Set up the register classes

addRegisterClass(MVT::i32, &Cpu0::CPURegsRegClass);

// must, computeRegisterProperties - Once all of the register classes are

// added, this allows us to compute derived properties we expose.

computeRegisterProperties(Subtarget.getRegisterInfo());

}

SDValue Cpu0SETargetLowering::LowerOperation(SDValue Op,

SelectionDAG &DAG) const {

return Cpu0TargetLowering::LowerOperation(Op, DAG);

}

const Cpu0TargetLowering *

llvm::createCpu0SETargetLowering(const Cpu0TargetMachine &TM,

const Cpu0Subtarget &STI) {

return new Cpu0SETargetLowering(TM, STI);

}

lbdex/chapters/Chapter3_1/Cpu0MachineFunction.h

//===-- Cpu0MachineFunctionInfo.h - Private data used for Cpu0 ----*- C++ -*-=//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file declares the Cpu0 specific subclass of MachineFunctionInfo.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0MACHINEFUNCTION_H

#define LLVM_LIB_TARGET_CPU0_CPU0MACHINEFUNCTION_H

#include "Cpu0Config.h"

#include "llvm/CodeGen/MachineFrameInfo.h"

#include "llvm/CodeGen/MachineFunction.h"

#include "llvm/CodeGen/MachineMemOperand.h"

#include "llvm/CodeGen/PseudoSourceValue.h"

#include "llvm/Target/TargetMachine.h"

#include <map>

namespace llvm {

//@1 {

/// Cpu0FunctionInfo - This class is derived from MachineFunction private

/// Cpu0 target-specific information for each MachineFunction.

class Cpu0FunctionInfo : public MachineFunctionInfo {

public:

Cpu0FunctionInfo(MachineFunction& MF)

: MF(MF),

VarArgsFrameIndex(0),

MaxCallFrameSize(0)

{}

~Cpu0FunctionInfo();

int getVarArgsFrameIndex() const { return VarArgsFrameIndex; }

void setVarArgsFrameIndex(int Index) { VarArgsFrameIndex = Index; }

private:

virtual void anchor();

MachineFunction& MF;

/// VarArgsFrameIndex - FrameIndex for start of varargs area.

int VarArgsFrameIndex;

unsigned MaxCallFrameSize;

};

//@1 }

} // end of namespace llvm

#endif // CPU0_MACHINE_FUNCTION_INFO_H

lbdex/chapters/Chapter3_1/Cpu0MachineFunction.cpp

//===-- Cpu0MachineFunctionInfo.cpp - Private data used for Cpu0 ----------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

#include "Cpu0MachineFunction.h"

#include "Cpu0InstrInfo.h"

#include "Cpu0Subtarget.h"

#include "llvm/IR/Function.h"

#include "llvm/CodeGen/MachineInstrBuilder.h"

#include "llvm/CodeGen/MachineRegisterInfo.h"

using namespace llvm;

bool FixGlobalBaseReg;

Cpu0FunctionInfo::~Cpu0FunctionInfo() {}

void Cpu0FunctionInfo::anchor() { }

lbdex/chapters/Chapter3_1/MCTargetDesc/Cpu0ABIInfo.h

//===---- Cpu0ABIInfo.h - Information about CPU0 ABI's --------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_MCTARGETDESC_CPU0ABIINFO_H

#define LLVM_LIB_TARGET_CPU0_MCTARGETDESC_CPU0ABIINFO_H

#include "Cpu0Config.h"

#include "llvm/ADT/ArrayRef.h"

#include "llvm/ADT/Triple.h"

#include "llvm/IR/CallingConv.h"

#include "llvm/MC/MCRegisterInfo.h"

namespace llvm {

class MCTargetOptions;

class StringRef;

class TargetRegisterClass;

class Cpu0ABIInfo {

public:

enum class ABI { Unknown, O32, S32 };

protected:

ABI ThisABI;

public:

Cpu0ABIInfo(ABI ThisABI) : ThisABI(ThisABI) {}

static Cpu0ABIInfo Unknown() { return Cpu0ABIInfo(ABI::Unknown); }

static Cpu0ABIInfo O32() { return Cpu0ABIInfo(ABI::O32); }

static Cpu0ABIInfo S32() { return Cpu0ABIInfo(ABI::S32); }

static Cpu0ABIInfo computeTargetABI();

bool IsKnown() const { return ThisABI != ABI::Unknown; }

bool IsO32() const { return ThisABI == ABI::O32; }

bool IsS32() const { return ThisABI == ABI::S32; }

ABI GetEnumValue() const { return ThisABI; }

/// The registers to use for byval arguments.

const ArrayRef<MCPhysReg> GetByValArgRegs() const;

/// The registers to use for the variable argument list.

const ArrayRef<MCPhysReg> GetVarArgRegs() const;

/// Obtain the size of the area allocated by the callee for arguments.

/// CallingConv::FastCall affects the value for O32.

unsigned GetCalleeAllocdArgSizeInBytes(CallingConv::ID CC) const;

/// Ordering of ABI's

/// Cpu0GenSubtargetInfo.inc will use this to resolve conflicts when given

/// multiple ABI options.

bool operator<(const Cpu0ABIInfo Other) const {

return ThisABI < Other.GetEnumValue();

}

unsigned GetStackPtr() const;

unsigned GetFramePtr() const;

unsigned GetNullPtr() const;

unsigned GetEhDataReg(unsigned I) const;

int EhDataRegSize() const;

};

}

#endif

lbdex/chapters/Chapter3_1/MCTargetDesc/Cpu0ABIInfo.cpp

//===---- Cpu0ABIInfo.cpp - Information about CPU0 ABI's ------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

#include "Cpu0Config.h"

#include "Cpu0ABIInfo.h"

#include "Cpu0RegisterInfo.h"

#include "llvm/ADT/StringRef.h"

#include "llvm/ADT/StringSwitch.h"

#include "llvm/MC/MCTargetOptions.h"

#include "llvm/Support/CommandLine.h"

using namespace llvm;

static cl::opt<bool>

EnableCpu0S32Calls("cpu0-s32-calls", cl::Hidden,

cl::desc("CPU0 S32 call: use stack only to pass arguments.\

"), cl::init(false));

namespace {

static const MCPhysReg O32IntRegs[4] = {Cpu0::A0, Cpu0::A1};

static const MCPhysReg S32IntRegs = {};

}

const ArrayRef<MCPhysReg> Cpu0ABIInfo::GetByValArgRegs() const {

if (IsO32())

return makeArrayRef(O32IntRegs);

if (IsS32())

return makeArrayRef(S32IntRegs);

llvm_unreachable("Unhandled ABI");

}

const ArrayRef<MCPhysReg> Cpu0ABIInfo::GetVarArgRegs() const {

if (IsO32())

return makeArrayRef(O32IntRegs);

if (IsS32())

return makeArrayRef(S32IntRegs);

llvm_unreachable("Unhandled ABI");

}

unsigned Cpu0ABIInfo::GetCalleeAllocdArgSizeInBytes(CallingConv::ID CC) const {

if (IsO32())

return CC != 0;

if (IsS32())

return 0;

llvm_unreachable("Unhandled ABI");

}

Cpu0ABIInfo Cpu0ABIInfo::computeTargetABI() {

Cpu0ABIInfo abi(ABI::Unknown);

if (EnableCpu0S32Calls)

abi = ABI::S32;

else

abi = ABI::O32;

// Assert exactly one ABI was chosen.

assert(abi.ThisABI != ABI::Unknown);

return abi;

}

unsigned Cpu0ABIInfo::GetStackPtr() const {

return Cpu0::SP;

}

unsigned Cpu0ABIInfo::GetFramePtr() const {

return Cpu0::FP;

}

unsigned Cpu0ABIInfo::GetNullPtr() const {

return Cpu0::ZERO;

}

unsigned Cpu0ABIInfo::GetEhDataReg(unsigned I) const {

static const unsigned EhDataReg[] = {

Cpu0::A0, Cpu0::A1

};

return EhDataReg[I];

}

int Cpu0ABIInfo::EhDataRegSize() const {

if (ThisABI == ABI::S32)

return 0;

else

return 2;

}

lbdex/chapters/Chapter3_1/Cpu0Subtarget.h

#include "Cpu0FrameLowering.h"

#include "Cpu0ISelLowering.h"

#include "Cpu0InstrInfo.h"

#include "llvm/CodeGen/SelectionDAGTargetInfo.h"

#include "llvm/CodeGen/TargetSubtargetInfo.h"

#include "llvm/IR/DataLayout.h"

#include "llvm/MC/MCInstrItineraries.h"

#include <string>

#define GET_SUBTARGETINFO_HEADER

#include "Cpu0GenSubtargetInfo.inc"

namespace llvm {

class StringRef;

class Cpu0TargetMachine;

class Cpu0Subtarget : public Cpu0GenSubtargetInfo {

virtual void anchor();

public:

bool HasChapterDummy;

bool HasChapterAll;

bool hasChapter3_1() const {

#if CH >= CH3_1

return true;

#else

return false;

#endif

}

bool hasChapter3_2() const {

#if CH >= CH3_2

return true;

#else

return false;

#endif

}

bool hasChapter3_3() const {

#if CH >= CH3_3

return true;

#else

return false;

#endif

}

bool hasChapter3_4() const {

#if CH >= CH3_4

return true;

#else

return false;

#endif

}

bool hasChapter3_5() const {

#if CH >= CH3_5

return true;

#else

return false;

#endif

}

bool hasChapter4_1() const {

#if CH >= CH4_1

return true;

#else

return false;

#endif

}

bool hasChapter4_2() const {

#if CH >= CH4_2

return true;

#else

return false;

#endif

}

bool hasChapter5_1() const {

#if CH >= CH5_1

return true;

#else

return false;

#endif

}

bool hasChapter6_1() const {

#if CH >= CH6_1

return true;

#else

return false;

#endif

}

bool hasChapter7_1() const {

#if CH >= CH7_1

return true;

#else

return false;

#endif

}

bool hasChapter8_1() const {

#if CH >= CH8_1

return true;

#else

return false;

#endif

}

bool hasChapter8_2() const {

#if CH >= CH8_2

return true;

#else

return false;

#endif

}

bool hasChapter9_1() const {

#if CH >= CH9_1

return true;

#else

return false;

#endif

}

bool hasChapter9_2() const {

#if CH >= CH9_2

return true;

#else

return false;

#endif

}

bool hasChapter9_3() const {

#if CH >= CH9_3

return true;

#else

return false;

#endif

}

bool hasChapter10_1() const {

#if CH >= CH10_1

return true;

#else

return false;

#endif

}

bool hasChapter11_1() const {

#if CH >= CH11_1

return true;

#else

return false;

#endif

}

bool hasChapter11_2() const {

#if CH >= CH11_2

return true;

#else

return false;

#endif

}

bool hasChapter12_1() const {

#if CH >= CH12_1

return true;

#else

return false;

#endif

}

protected:

enum Cpu0ArchEnum {

Cpu032I,

Cpu032II

};

// Cpu0 architecture version

Cpu0ArchEnum Cpu0ArchVersion;

// IsLittle - The target is Little Endian

bool IsLittle;

bool EnableOverflow;

// HasCmp - cmp instructions.

bool HasCmp;

// HasSlt - slt instructions.

bool HasSlt;

InstrItineraryData InstrItins;

const Cpu0TargetMachine &TM;

Triple TargetTriple;

const SelectionDAGTargetInfo TSInfo;

std::unique_ptr<const Cpu0InstrInfo> InstrInfo;

std::unique_ptr<const Cpu0FrameLowering> FrameLowering;

std::unique_ptr<const Cpu0TargetLowering> TLInfo;

public:

bool isPositionIndependent() const;

const Cpu0ABIInfo &getABI() const;

/// This constructor initializes the data members to match that

/// of the specified triple.

Cpu0Subtarget(const Triple &TT, StringRef CPU, StringRef FS,

bool little, const Cpu0TargetMachine &_TM);

//- Vitual function, must have

/// ParseSubtargetFeatures - Parses features string setting specified

/// subtarget options. Definition of function is auto generated by tblgen.

void ParseSubtargetFeatures(StringRef CPU, StringRef TuneCPU, StringRef FS);

bool isLittle() const { return IsLittle; }

bool hasCpu032I() const { return Cpu0ArchVersion >= Cpu032I; }

bool isCpu032I() const { return Cpu0ArchVersion == Cpu032I; }

bool hasCpu032II() const { return Cpu0ArchVersion >= Cpu032II; }

bool isCpu032II() const { return Cpu0ArchVersion == Cpu032II; }

/// Features related to the presence of specific instructions.

bool enableOverflow() const { return EnableOverflow; }

bool disableOverflow() const { return !EnableOverflow; }

bool hasCmp() const { return HasCmp; }

bool hasSlt() const { return HasSlt; }

bool abiUsesSoftFloat() const;

bool enableLongBranchPass() const {

return hasCpu032II();

}

unsigned stackAlignment() const { return 8; }

Cpu0Subtarget &initializeSubtargetDependencies(StringRef CPU, StringRef FS,

const TargetMachine &TM);

const SelectionDAGTargetInfo *getSelectionDAGInfo() const override {

return &TSInfo;

}

const Cpu0InstrInfo *getInstrInfo() const override { return InstrInfo.get(); }

const TargetFrameLowering *getFrameLowering() const override {

return FrameLowering.get();

}

const Cpu0RegisterInfo *getRegisterInfo() const override {

return &InstrInfo->getRegisterInfo();

}

const Cpu0TargetLowering *getTargetLowering() const override {

return TLInfo.get();

}

const InstrItineraryData *getInstrItineraryData() const override {

return &InstrItins;

}

};

} // End llvm namespace

#endif

lbdex/chapters/Chapter3_1/Cpu0Subtarget.cpp

//===-- Cpu0Subtarget.cpp - Cpu0 Subtarget Information --------------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file implements the Cpu0 specific subclass of TargetSubtargetInfo.

//

//===----------------------------------------------------------------------===//

#include "Cpu0Subtarget.h"

#include "Cpu0MachineFunction.h"

#include "Cpu0.h"

#include "Cpu0RegisterInfo.h"

#include "Cpu0TargetMachine.h"

#include "llvm/IR/Attributes.h"

#include "llvm/IR/Function.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Support/ErrorHandling.h"

#include "llvm/Support/TargetRegistry.h"

using namespace llvm;

#define DEBUG_TYPE "cpu0-subtarget"

#define GET_SUBTARGETINFO_TARGET_DESC

#define GET_SUBTARGETINFO_CTOR

#include "Cpu0GenSubtargetInfo.inc"

extern bool FixGlobalBaseReg;

void Cpu0Subtarget::anchor() { }

//@1 {

Cpu0Subtarget::Cpu0Subtarget(const Triple &TT, StringRef CPU,

StringRef FS, bool little,

const Cpu0TargetMachine &_TM) :

//@1 }

// Cpu0GenSubtargetInfo will display features by llc -march=cpu0 -mcpu=help

Cpu0GenSubtargetInfo(TT, CPU, /*TuneCPU*/ CPU, FS),

IsLittle(little), TM(_TM), TargetTriple(TT), TSInfo(),

InstrInfo(

Cpu0InstrInfo::create(initializeSubtargetDependencies(CPU, FS, TM))),

FrameLowering(Cpu0FrameLowering::create(*this)),

TLInfo(Cpu0TargetLowering::create(TM, *this)) {

}

bool Cpu0Subtarget::isPositionIndependent() const {

return TM.isPositionIndependent();

}

Cpu0Subtarget &

Cpu0Subtarget::initializeSubtargetDependencies(StringRef CPU, StringRef FS,

const TargetMachine &TM) {

if (TargetTriple.getArch() == Triple::cpu0 || TargetTriple.getArch() == Triple::cpu0el) {

if (CPU.empty() || CPU == "generic") {

CPU = "cpu032II";

}

else if (CPU == "help") {

CPU = "";

return *this;

}

else if (CPU != "cpu032I" && CPU != "cpu032II") {

CPU = "cpu032II";

}

}

else {

errs() << "!!!Error, TargetTriple.getArch() = " << TargetTriple.getArch()

<< "CPU = " << CPU << "\n";

exit(0);

}

if (CPU == "cpu032I")

Cpu0ArchVersion = Cpu032I;

else if (CPU == "cpu032II")

Cpu0ArchVersion = Cpu032II;

if (isCpu032I()) {

HasCmp = true;

HasSlt = false;

}

else if (isCpu032II()) {

HasCmp = false;

HasSlt = true;

}

else {

errs() << "-mcpu must be empty(default:cpu032II), cpu032I or cpu032II" << "\n";

}

// Parse features string.

ParseSubtargetFeatures(CPU, /*TuneCPU*/ CPU, FS);

// Initialize scheduling itinerary for the specified CPU.

InstrItins = getInstrItineraryForCPU(CPU);

return *this;

}

bool Cpu0Subtarget::abiUsesSoftFloat() const {

// return TM->Options.UseSoftFloat;

return true;

}

const Cpu0ABIInfo &Cpu0Subtarget::getABI() const { return TM.getABI(); }

lbdex/chapters/Chapter3_1/Cpu0RegisterInfo.h

//===-- Cpu0RegisterInfo.h - Cpu0 Register Information Impl -----*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the Cpu0 implementation of the TargetRegisterInfo class.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0REGISTERINFO_H

#define LLVM_LIB_TARGET_CPU0_CPU0REGISTERINFO_H

#include "Cpu0Config.h"

#include "Cpu0.h"

#include "llvm/CodeGen/TargetRegisterInfo.h"

#define GET_REGINFO_HEADER

#include "Cpu0GenRegisterInfo.inc"

namespace llvm {

class Cpu0Subtarget;

class TargetInstrInfo;

class Type;

class Cpu0RegisterInfo : public Cpu0GenRegisterInfo {

protected:

const Cpu0Subtarget &Subtarget;

public:

Cpu0RegisterInfo(const Cpu0Subtarget &Subtarget);

const MCPhysReg *getCalleeSavedRegs(const MachineFunction *MF) const override;

const uint32_t *getCallPreservedMask(const MachineFunction &MF,

CallingConv::ID) const override;

BitVector getReservedRegs(const MachineFunction &MF) const override;

bool requiresRegisterScavenging(const MachineFunction &MF) const override;

bool trackLivenessAfterRegAlloc(const MachineFunction &MF) const override;

/// Stack Frame Processing Methods

void eliminateFrameIndex(MachineBasicBlock::iterator II,

int SPAdj, unsigned FIOperandNum,

RegScavenger *RS = nullptr) const override;

/// Debug information queries.

Register getFrameRegister(const MachineFunction &MF) const override;

/// \brief Return GPR register class.

virtual const TargetRegisterClass *intRegClass(unsigned Size) const = 0;

};

} // end namespace llvm

#endif

lbdex/chapters/Chapter3_1/Cpu0RegisterInfo.cpp

//===-- Cpu0RegisterInfo.cpp - CPU0 Register Information -== --------------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the CPU0 implementation of the TargetRegisterInfo class.

//

//===----------------------------------------------------------------------===//

#define DEBUG_TYPE "cpu0-reg-info"

#include "Cpu0RegisterInfo.h"

#include "Cpu0.h"

#include "Cpu0Subtarget.h"

#include "Cpu0MachineFunction.h"

#include "llvm/IR/Function.h"

#include "llvm/IR/Type.h"

#include "llvm/Support/CommandLine.h"

#include "llvm/Support/Debug.h"

#include "llvm/Support/ErrorHandling.h"

#include "llvm/Support/raw_ostream.h"

#define GET_REGINFO_TARGET_DESC

#include "Cpu0GenRegisterInfo.inc"

using namespace llvm;

Cpu0RegisterInfo::Cpu0RegisterInfo(const Cpu0Subtarget &ST)

: Cpu0GenRegisterInfo(Cpu0::LR), Subtarget(ST) {}

//===----------------------------------------------------------------------===//

// Callee Saved Registers methods

//===----------------------------------------------------------------------===//

/// Cpu0 Callee Saved Registers

// In Cpu0CallConv.td,

// def CSR_O32 : CalleeSavedRegs<(add LR, FP,

// (sequence "S%u", 2, 0))>;

// llc create CSR_O32_SaveList and CSR_O32_RegMask from above defined.

const MCPhysReg *

Cpu0RegisterInfo::getCalleeSavedRegs(const MachineFunction *MF) const {

return CSR_O32_SaveList;

}

const uint32_t *

Cpu0RegisterInfo::getCallPreservedMask(const MachineFunction &MF,

CallingConv::ID) const {

return CSR_O32_RegMask;

}

// pure virtual method

//@getReservedRegs {

BitVector Cpu0RegisterInfo::

getReservedRegs(const MachineFunction &MF) const {

//@getReservedRegs body {

static const uint16_t ReservedCPURegs[] = {

Cpu0::ZERO, Cpu0::AT, Cpu0::SP, Cpu0::LR, /*Cpu0::SW, */Cpu0::PC

};

BitVector Reserved(getNumRegs());

for (unsigned I = 0; I < array_lengthof(ReservedCPURegs); ++I)

Reserved.set(ReservedCPURegs[I]);

return Reserved;

}

//@eliminateFrameIndex {

//- If no eliminateFrameIndex(), it will hang on run.

// pure virtual method

// FrameIndex represent objects inside a abstract stack.

// We must replace FrameIndex with an stack/frame pointer

// direct reference.

void Cpu0RegisterInfo::

eliminateFrameIndex(MachineBasicBlock::iterator II, int SPAdj,

unsigned FIOperandNum, RegScavenger *RS) const {

}

//}

bool

Cpu0RegisterInfo::requiresRegisterScavenging(const MachineFunction &MF) const {

return true;

}

bool

Cpu0RegisterInfo::trackLivenessAfterRegAlloc(const MachineFunction &MF) const {

return true;

}

// pure virtual method

Register Cpu0RegisterInfo::

getFrameRegister(const MachineFunction &MF) const {

const TargetFrameLowering *TFI = MF.getSubtarget().getFrameLowering();

return TFI->hasFP(MF) ? (Cpu0::FP) :

(Cpu0::SP);

}

lbdex/chapters/Chapter3_1/Cpu0SERegisterInfo.h

//===-- Cpu0SERegisterInfo.h - Cpu032 Register Information ------*- C++ -*-===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the Cpu032/64 implementation of the TargetRegisterInfo

// class.

//

//===----------------------------------------------------------------------===//

#ifndef LLVM_LIB_TARGET_CPU0_CPU0SEREGISTERINFO_H

#define LLVM_LIB_TARGET_CPU0_CPU0SEREGISTERINFO_H

#include "Cpu0Config.h"

#include "Cpu0RegisterInfo.h"

namespace llvm {

class Cpu0SEInstrInfo;

class Cpu0SERegisterInfo : public Cpu0RegisterInfo {

public:

Cpu0SERegisterInfo(const Cpu0Subtarget &Subtarget);

const TargetRegisterClass *intRegClass(unsigned Size) const override;

};

} // end namespace llvm

#endif

lbdex/chapters/Chapter3_1/Cpu0SERegisterInfo.cpp

//===-- Cpu0SERegisterInfo.cpp - CPU0 Register Information ------== -------===//

//

// The LLVM Compiler Infrastructure

//

// This file is distributed under the University of Illinois Open Source

// License. See LICENSE.TXT for details.

//

//===----------------------------------------------------------------------===//

//

// This file contains the CPU0 implementation of the TargetRegisterInfo

// class.

//

//===----------------------------------------------------------------------===//

#include "Cpu0SERegisterInfo.h"

using namespace llvm;

#define DEBUG_TYPE "cpu0-reg-info"

Cpu0SERegisterInfo::Cpu0SERegisterInfo(const Cpu0Subtarget &ST)

: Cpu0RegisterInfo(ST) {}

const TargetRegisterClass *

Cpu0SERegisterInfo::intRegClass(unsigned Size) const {

return &Cpu0::CPURegsRegClass;

}

build/lib/Target/Cpu0/Cpu0GenInstInfo.inc

//- Cpu0GenInstInfo.inc which generate from Cpu0InstrInfo.td

#ifdef GET_INSTRINFO_HEADER

#undef GET_INSTRINFO_HEADER

namespace llvm {

struct Cpu0GenInstrInfo : public TargetInstrInfoImpl {

explicit Cpu0GenInstrInfo(int SO = -1, int DO = -1);

};

} // End llvm namespace

#endif // GET_INSTRINFO_HEADER

#define GET_INSTRINFO_HEADER

#include "Cpu0GenInstrInfo.inc"

//- Cpu0InstInfo.h

class Cpu0InstrInfo : public Cpu0GenInstrInfo {

Cpu0TargetMachine &TM;

public:

explicit Cpu0InstrInfo(Cpu0TargetMachine &TM);

};

Fig. 20 Cpu0 backend class access link¶

Chapter3_1 adds most of the Cpu0 backend classes. The code in Chapter3_1 can be summarized in Fig. 20.

The Cpu0Subtarget class provides interfaces such as getInstrInfo(), getFrameLowering(), etc., to access other Cpu0 classes. Most classes (like Cpu0InstrInfo, Cpu0RegisterInfo, etc.) contain a Subtarget reference member, allowing them to access other classes through the Cpu0Subtarget interface.

If a backend module does not have a Subtarget reference, these classes can still access the Subtarget class through Cpu0TargetMachine (typically referred to as TM) using:

static_cast<Cpu0TargetMachine &>(TM).getSubtargetImpl()

Once the Subtarget class is obtained, the backend code can access other classes through it.

For classes named Cpu0SExx, they represent the standard 32-bit class. This naming convention follows the LLVM 3.5 Mips backend style. The Mips backend uses Mips16, MipsSE, and Mips64 file/class names to define classes for 16-bit, 32-bit, and 64-bit architectures, respectively.

Since Cpu0Subtarget creates Cpu0InstrInfo, Cpu0RegisterInfo, etc., in its constructor, it can provide class references through the interfaces shown in Fig. 20.

Fig. 21 below illustrates the Cpu0 TableGen inheritance relationship.

In the previous chapter, we mentioned that backend classes can include TableGen-generated classes and inherit from them. All TableGen-generated classes for the Cpu0 backend are located in:

build/lib/Target/Cpu0/*.inc

Through C++ inheritance, TableGen provides backend developers with a flexible way to utilize its generated code. Developers also have the opportunity to override functions if needed.

Fig. 21 Cpu0 classes inherited from TableGen-generated files¶

Since LLVM has a deep inheritance tree, it is not fully explored here. Benefiting from the inheritance tree structure, minimal code needs to be implemented in instruction, frame/stack, and DAG selection classes, as much of the functionality is already provided by their parent classes.

The llvm-tblgen tool generates Cpu0GenInstrInfo.inc based on the information in Cpu0InstrInfo.td.

Cpu0InstrInfo.h extracts the necessary code from Cpu0GenInstrInfo.inc by defining:

#define GET_INSTRINFO_HEADER

With TableGen, the backend code size is further reduced through the pattern matching theory of compiler development. This is explained in the “DAG” and “Instruction Selection” sections of the previous chapter.

The following is a code fragment from Cpu0GenInstrInfo.inc. Code between #ifdef GET_INSTRINFO_HEADER and #endif // GET_INSTRINFO_HEADER is extracted into Cpu0InstrInfo.h.

build/lib/Target/Cpu0/Cpu0GenInstInfo.inc

//- Cpu0GenInstInfo.inc which generate from Cpu0InstrInfo.td

#ifdef GET_INSTRINFO_HEADER

#undef GET_INSTRINFO_HEADER

namespace llvm {

struct Cpu0GenInstrInfo : public TargetInstrInfoImpl {

explicit Cpu0GenInstrInfo(int SO = -1, int DO = -1);

};

} // End llvm namespace

#endif // GET_INSTRINFO_HEADER

Reference web sites are here [1] [2].

Chapter3_1/CMakeLists.txt is modified with these new added *.cpp as follows,

lbdex/chapters/Chapter3_1/CMakeLists.txt

tablegen(LLVM Cpu0GenDAGISel.inc -gen-dag-isel)

tablegen(LLVM Cpu0GenCallingConv.inc -gen-callingconv)

Cpu0FrameLowering.cpp

Please take a look for Chapter3_1 code. After that, building Chapter3_1 by “#define CH CH3_1” in Cpu0Config.h as follows, and do building with cmake and make again.

~/llvm/test/llvm/lib/Target/Cpu0SetChapter.h

#define CH CH3_1

118-165-78-230:input Jonathan$ /Users/Jonathan/llvm/test/build/

bin/llc -march=cpu0 -relocation-model=pic -filetype=asm ch3.bc -o

ch3.cpu0.s

... Assertion failed: (MRI && "Unable to create reg info"), function initAsmInfo

...

With Chapter3_1 implementation, the Chapter2 error message “Could not allocate target machine!” has gone. The new error say that we have not Target AsmPrinter and asm register info. We will add it in next section.

With the implementation of Chapter3_1, the Chapter2 error message “Could not allocate target machine!” has been resolved. The new error indicates that we lack Target AsmPrinter and ASM register info. We will add these in the next section.

Chapter3_1 creates FeatureCpu032I and FeatureCpu032II for CPUs cpu032I and cpu032II, respectively. Additionally, it defines two more features: FeatureCmp and FeatureSlt.

To demonstrate instruction set design choices, this book introduces two CPUs. Readers will understand why MIPS CPUs use the SLT instruction instead of CMP after reading the later chapter, “Control Flow Statement”.

With the added support for cpu032I and cpu032II in Cpu0.td and Cpu0InstrInfo.td from Chapter3_1, running the command:

llc -march=cpu0 -mcpu=help

will display messages as follows:

JonathantekiiMac:input Jonathan$ /Users/Jonathan/llvm/test/

build/bin/llc -march=cpu0 -mcpu=help

Available CPUs for this target:

cpu032I - Select the cpu032I processor.

cpu032II - Select the cpu032II processor.

Available features for this target:

ch10_1 - Enable Chapter instructions..

ch11_1 - Enable Chapter instructions..

ch11_2 - Enable Chapter instructions..

ch14_1 - Enable Chapter instructions..

ch3_1 - Enable Chapter instructions..

ch3_2 - Enable Chapter instructions..

ch3_3 - Enable Chapter instructions..

ch3_4 - Enable Chapter instructions..

ch3_5 - Enable Chapter instructions..

ch4_1 - Enable Chapter instructions..

ch4_2 - Enable Chapter instructions..

ch5_1 - Enable Chapter instructions..

ch6_1 - Enable Chapter instructions..

ch7_1 - Enable Chapter instructions..

ch8_1 - Enable Chapter instructions..

ch8_2 - Enable Chapter instructions..

ch9_1 - Enable Chapter instructions..

ch9_2 - Enable Chapter instructions..

ch9_3 - Enable Chapter instructions..

chall - Enable Chapter instructions..

cmp - Enable 'cmp' instructions..

cpu032I - Cpu032I ISA Support.

cpu032II - Cpu032II ISA Support (slt).

o32 - Enable o32 ABI.

s32 - Enable s32 ABI.

slt - Enable 'slt' instructions..

Use +feature to enable a feature, or -feature to disable it.

For example, llc -mcpu=mycpu -mattr=+feature1,-feature2

...

When the user inputs -mcpu=cpu032I, the variable IsCpu032I from

Cpu0InstrInfo.td will be true since the function isCpu032I() defined

in Cpu0Subtarget.h returns true. This happens because Cpu0ArchVersion

is set to cpu032I in initializeSubtargetDependencies(), which is called

in the constructor. The variable CPU in the constructor is “cpu032I” when

the user inputs -mcpu=cpu032I.

Please note that the variable Cpu0ArchVersion must be initialized in

Cpu0Subtarget.cpp. Otherwise, Cpu0ArchVersion may hold an undefined value,

causing issues with isCpu032I() and isCpu032II(), which support

llc -mcpu=cpu032I and llc -mcpu=cpu032II, respectively.

The values of the variables HasCmp and HasSlt depend on Cpu0ArchVersion. The instructions slt, beq, etc., are supported only if HasSlt is true. Furthermore, HasSlt is true only when Cpu0ArchVersion is Cpu032II.

Similarly, Ch4_1, Ch4_2, etc., control the enabling or disabling of instruction definitions. Through Subtarget->hasChapter4_1(), which exists in both Cpu0.td and Cpu0Subtarget.h, predicates such as Ch4_1, defined in Cpu0InstrInfo.td, can be enabled or disabled.

For example, the shift-rotate instructions can be enabled by defining CH to be greater than or equal to CH4_1, as shown below:

lbdex/Cpu0/Cpu0InstrInfo.td

let Predicates = [Ch4_1] in {

class shift_rotate_reg<bits<8> op, bits<4> isRotate, string instr_asm,

SDNode OpNode, RegisterClass RC>:

FA<op, (outs GPROut:$ra), (ins RC:$rb, RC:$rc),

!strconcat(instr_asm, "\t$ra, $rb, $rc"),

[(set GPROut:$ra, (OpNode RC:$rb, RC:$rc))], IIAlu> {

let shamt = 0;

}

}

~/llvm/test/llvm/lib/Target/Cpu0SetChapter.h

#define CH CH4_1

On the contrary, it can be disabled by define it to less than CH4_1, for instance CH3_5, as follows,

~/llvm/test/llvm/lib/Target/Cpu0SetChapter.h

#define CH CH3_5

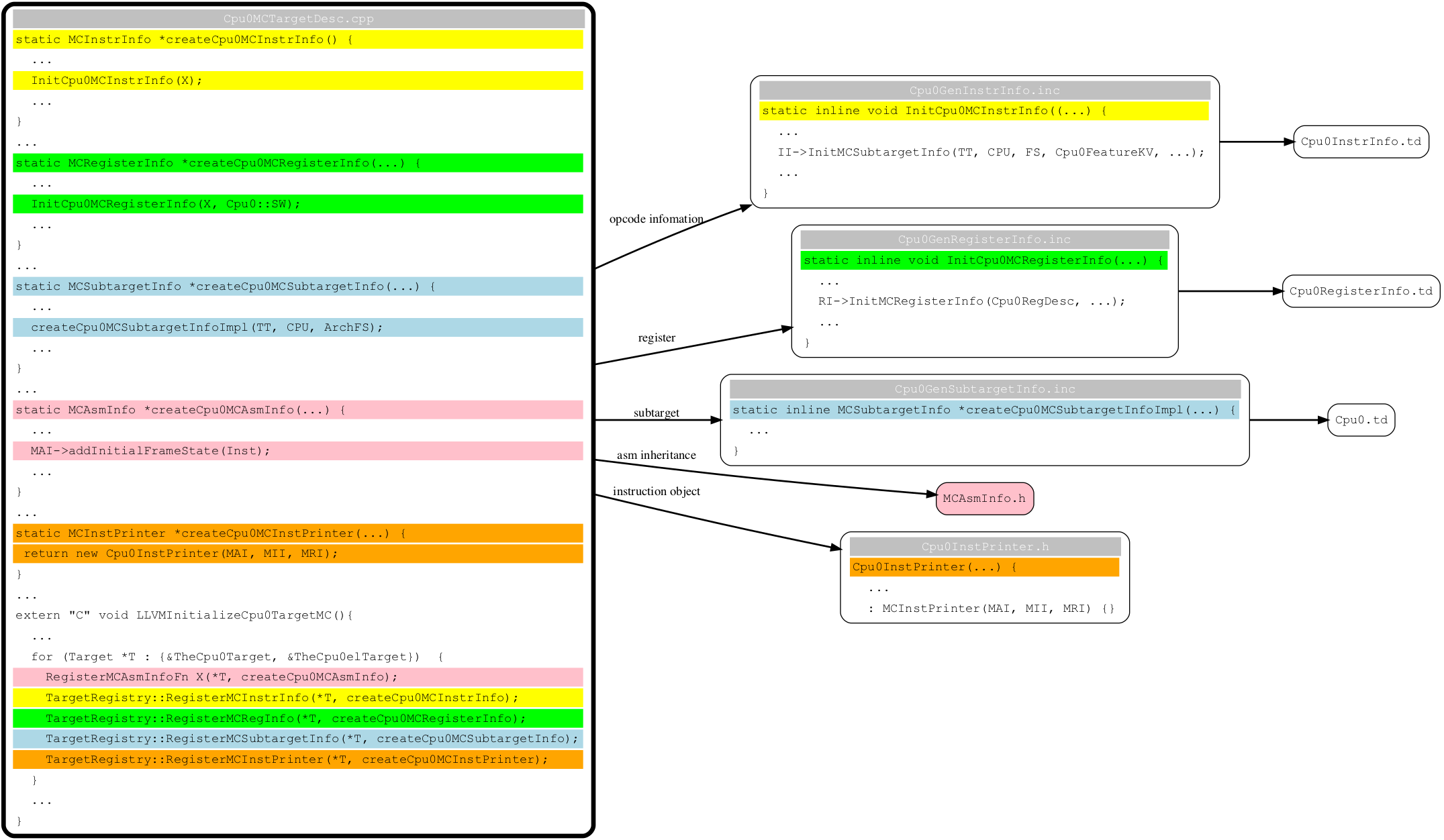

Add AsmPrinter¶

![digraph G {

rankdir=LR;

MCInst [style="filled,bold", fillcolor=lightgreen];

assembly [style="filled,bold", fillcolor=lightgreen];

"llvm-ir" -> DAG -> MachineInstr -> MCInst -> assembly;

}](_images/graphviz-a7c0e62c0fcbaec635c45fce36154e8cf8888d31.png)

Fig. 22 When “llc -filetype=asm”, Cpu0AsmPrinter extract MCInst from MachineInstr for asm encoding¶

As Fig. 22, because MachineInstr is a big class for opitmization and convertion in many passes. LLVM creates MCInst for encoding purpose in assembly and binary object.

Chapter3_2/ contains the Cpu0AsmPrinter definition.

lbdex/chapters/Chapter2/Cpu0.td